# 500MHz-2GHz BROADBAND POWER AMPLIFIER DESIGN BY NON-LINEAR MODELING METHODS

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF ÇANKAYA UNIVERSITY

BY GÖKALP ÜNAL

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN

ELECTRONIC AND COMMUNICATION ENGINEERING

SEPTEMBER 2009

# Title of the Thesis: 500MHz-2GHz Broadband Power Amplifier Design by Non-liner Modeling Methods

Submitted by Gökalp ÜNAL

Approval of the Graduate School of Natural and Applied Sciences, Çankaya University

Prof.Dr. Yahya Kemal BAYKAL

Acting Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Prof.Dr. Yahya Kemal BAYKAL Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof.Dr. Yahya Kemal BAYKAL Supervisor

**Examination Date**

: 01.09.2009

**Examining Committee Members:** Prof.Dr. Yahya Kemal BAYKAL

Assoc. Prof.Dr. Yusuf Ziya UMUL

Asist. Prof.Dr. Cem NAKİBOĞLU

(Çankaya Univ.) C. Walen fr (Çankaya Univ.) (Gazi Univ.)

## STATEMENT OF NON-PLAGIARISM

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

> Name, Last Name : Signature Date

:

:

Gökalp ÜNAI 01.09.2009

## ABSTRACT

## 500MHz-2GHz BROADBAND POWER AMPLIFIER DESIGN BY NON-LINEAR MODELING METHODS

ÜNAL, Gökalp

M.S.C., Department of Electronics and Communication Engineering Supervisor: Prof.Dr. Yahya Kemal BAYKAL

SEPTEMBER 2009, 141 pages

This thesis presents the design methods of 500MHz-2GHz broadband RF power amplifier. First of all, RF power transistor technologies are searched and the most suitable one is chosen according to its operation of frequency band, maximum output power, efficiency and cost features. The amplifier is designed as it has two stages, and in both stages LDMOS transistor technology is used as RF power transistors. Large signal models for the LDMOS devices are used in simulation, and according to the measurement results, the circuitry in simulation is tried to model at nonlinear conditions. A broadband RF-Choke structure with a new technique is developed to obtain high DC isolation and low RF loss over the desired bandwidth. Input and output matching networks and shunt feedback topology are introduced to fulfill the bandwidth requirements. Typical values of 20dB power gain, 37dBm output power, have been achieved at the most part of the frequency band of 500MHz-2GHz.

Keywords: RF, power amplifier, RF-Choke, transistor technologies, non-linear modeling

# DOĞRUSAL OLMAYAN MODELLEME YÖNTEMİYLE 500MHz-2GHz GENİŞ BANTLI GÜÇ YÜKSELTEÇ TASARIMI

ÜNAL, Gökalp

Yüksek Lisans, Elektronik ve Haberleşme Mühendisliği Anabilim Dalı Tez Yöneticisi: Prof.Dr. Yahya Kemal BAYKAL

EYLÜL 2009, 141 sayfa

Bu tez 500MHz-2GHz geniş bantlı RF güç yükseltecin tasarım yöntemlerini göstermektedir. İlk olarak, RF güç transistör teknolojileri araştırıldı ve içlerinden çalışma bandına, en yüksek çıkış gücüne, verimliliğine ve fiyatına göre en uygun olanı seçildi. Güç yükselteç iki aşama olacak şekilde tasarlandı ve bu iki aşamada da RF güç transistörü olarak LDMOS teknolojisi kullanıldı. Benzetimde LDMOS elemanları için yüksek sinyal modelleri kullanıldı ve ölçüm sonuçlarına göre benzetimdeki devre doğrusal olmayan durumda modellenmeye çalışıldı. İstenen bantta yüksek doğru akım yalıtımı ve düşük RF kaybı elde edebilmek için yeni bir teknik ile geniş bantlı RF yüksek frekans söndürme bobini yapısı geliştirildi. Bütün banttaki gereksinimleri sağlamak için giriş ve çıkış uyumlama devreleri ve paralel geri besleme yapısı kullanıldı. 500MHz-2GHz bandının büyük bir kısmında, tipik değerler olarak 20dB güç kazancı ve 37dBm çıkış gücü elde edildi.

Anahtar Kelimeler: RF, güç yükselteç, RF yüksek frekans söndürme bobini, transistör teknolojileri, doğrusal olmayan modelleme

## ACKNOWLEDGEMENTS

I am in great dept to my supervisor Prof. Dr. Yahya Kemal BAYKAL for his support and guidance throughout this thesis study.

I would like to express my thanks to my instructor Göker ŞENER for his precious guidance, friendly encouragement and valuable recommendations.

I am grateful to İbrahim Atak ÖZKAN for his support throughout the development and improvement of this thesis.

I am also grateful to Aselsan Electronics Industries Inc. for the resources and facilities that I have used throughout the thesis.

I would also like to thank Turkish Scientific and Technological Research Council (TUBİTAK) for their financial assistance during my graduate study.

Thanks a lot to my family and all my friends for their great encouragement and their valuable help to accomplish this work.

And special thanks to my fiancée for her support and patience without expecting any response; she always trusts me, and I am really grateful to her.

# **TABLE OF CONTENTS**

| STATEMENT OF NON-PLAGIARISM                               | iii |

|-----------------------------------------------------------|-----|

| ABSTRACT                                                  | iv  |

| ÖZ                                                        | v   |

| ACKNOWLEDGEMENTS                                          | vi  |

| TABLE OF CONTENTS                                         | vii |

| LIST OF TABLES                                            | xi  |

| LIST OF FIGURES                                           | xii |

| CHAPTERS:                                                 |     |

| 1. INTRODUCTION                                           | 1   |

| 2. HIGH POWER RF TRANSISTOR AMPLIFIER DESIGN              | 2   |

| 2.1. LOAD LINE ANALYSIS                                   | 2   |

| 2.2. STABILITY CONSIDERATIONS                             | 4   |

| 2.3. IMPEDANCE MATCHING NETWORKS                          | 7   |

| 2.4. LARGE SIGNAL IMPEDANCE MATCHING                      | 16  |

| 2.5. INTERMODULATION DISTORTION & 1-dB COMPRESSION POINT. | 20  |

| 2.6. EFFICIENCY                                           | 23  |

| 2.7. SUMMARY                                              | 24  |

| 3. TRANSISTOR TECHNOLOGIES                                | 26  |

| 3.1. SILICON                                              | 27  |

| 3.1.1. Silicon CMOS                                       | 27  |

| 3.1.2. Silicon LDMOS                                      | 28  |

| 3.2. GALLIUM ARSENIDE (GaAs)                              | 32  |

| 3.2.1. GaAs MESFET                                        | 35  |

| 3.2.2. GaAs PHEMT                                         | 36  |

| 3.2.3. GaAs MHEMT                                         | 37  |

| 3.2.4. GaAs HBT                                          |      |

|----------------------------------------------------------|------|

| 3.3. INDIUM PHOSPHIDE                                    | 39   |

| 3.3.1. Indium Phosphide HEMT                             | 39   |

| 3.3.2. Indium Phosphide HBT                              | 40   |

| 3.4. SILICON CARBIDE (SiC)                               | 40   |

| 3.4.1. Silicon Carbide MESFET                            | 43   |

| 3.4.2. Silicon Carbide LDMOS                             | 43   |

| 3.5. Silicon Germanium HBT                               | 44   |

| 3.6. GaN HEMT                                            | 45   |

| 4. SINGLE STAGE DESIGN OF MW6S004NT1 TRANSISTOR          | 47   |

| 4.1. INTRODUCTION                                        | 47   |

| 4.2. CRITERIAS OF CHOSING FREESCALE MW6S004NT1 TRANSISTO | R 52 |

| 4.3. SIMULATIONS & MEASUREMENTS                          | 54   |

| 4.3.1. DC BIASING                                        | 54   |

| 4.3.2. DC BIASING NETWORK (DESIGN OF CHOKE)              | 56   |

| 4.3.3. SIMULATION METHODS                                | 66   |

| 4.3.3.1. MODEL VERIFING                                  | 66   |

| 4.3.3.2. STABILTY                                        | 71   |

| 4.3.3.3. SCATTERING PARAMETERS                           | 75   |

| 4.3.3.4. INTERMODULATION DISTORTION                      | 78   |

| 4.3.3.5. EFFICIENCY                                      | 81   |

| 4.3.3.6. 1dB COMPRESSION POINT                           | 82   |

| 4.3.4. MEASUREMENT METHODS                               | 83   |

| 4.3.4.1. STABILITY                                       | 83   |

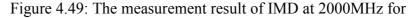

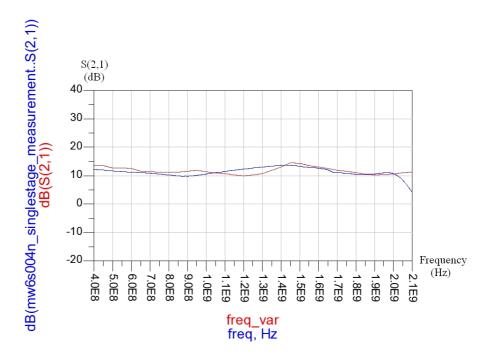

| 4.3.4.2. SCATTERING PARAMETERS                           | 83   |

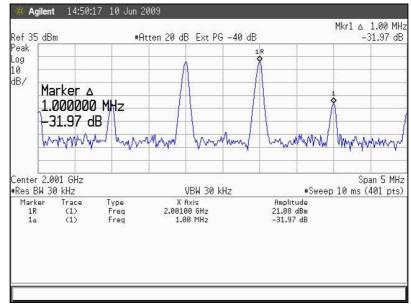

| 4.3.4.3. INTERMODULATION DISTORTION                      | 87   |

| 4.3.4.4. EFFICIENCY                                      | 90   |

| 4.3.4.5. 1dB COMPRESSION POINT                           | 90   |

| 4.3.5. COMPARISON BETWEEN SIMULATION & MEASUREMENT       |      |

| RESULTS                                                  | 91   |

| 4.3.5.1. STABILITY                                 | 91  |

|----------------------------------------------------|-----|

| 4.3.5.2. SCATTERING PARAMETERS                     | 91  |

| 4.3.5.3. INTERMODULATION DISTORTION                | 94  |

| 4.4. SUMMARY                                       | 95  |

| 5. MULTI STAGE DESIGN OF FREESCALE MW6S004NT1 &    |     |

| NXP BLF3G21-6 TRANSISTORS                          | 96  |

| 5.1. INTRODUCTION                                  | 96  |

| 5.2. CRITERIAS OF CHOSING NXP BLF3G21-6 TRANSISTOR |     |

| 5.3. SIMILATIONS & MEASUREMENTS                    |     |

| 5.3.1. DC BIASING                                  |     |

| 5.3.2. DC BIASING NETWORK (DESIGN OF CHOKE)        |     |

| 5.3.3. SIMULATION METHODS                          |     |

| 5.3.3.1. MODEL VERIFING                            |     |

| 5.3.3.2. STABILITY                                 |     |

| 5.3.3.3. SCATTERING PARAMETERS                     |     |

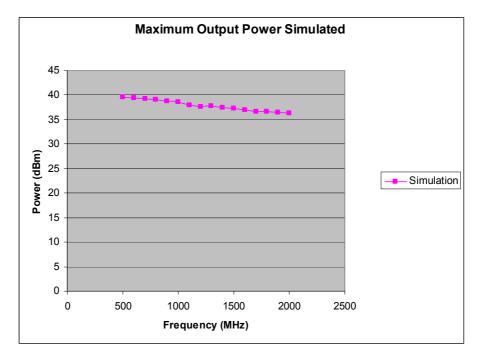

| 5.3.3.4. MAXIMUM OUTPUT POWER                      | 111 |

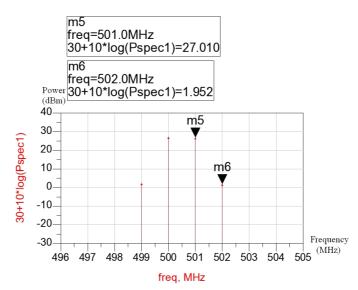

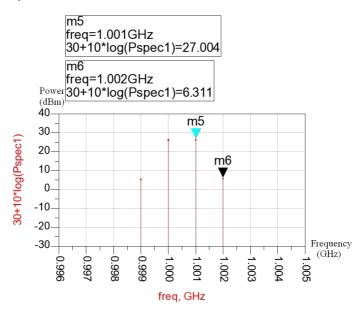

| 5.3.3.5. INTERMODULATION DISTORTION                | 112 |

| 5.3.3.6. EFFICIENCY                                | 116 |

| 5.3.3.7. 1dB COMPRESSION POINT                     | 118 |

| 5.3.4. MEASUREMENT METHODS                         | 119 |

| 5.3.4.1. STABILITY                                 | 119 |

| 5.3.4.2. SCATTERING PARAMETERS                     | 119 |

| 5.3.4.3. MAXIMUM OUTPUT POWER                      |     |

| 5.3.4.4. INTERMODULATION DISTORTION                | 124 |

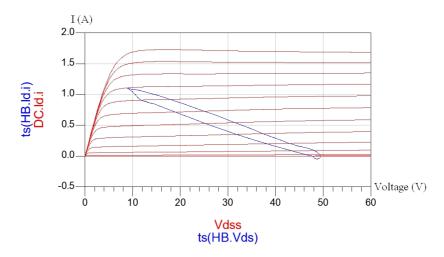

| 5.3.4.5. EFFICIENCY                                |     |

| 5.3.4.6. Pout vs. Pin CURVES                       |     |

| 5.3.5. COMPRESSION BETWEEN SIMULATION &            |     |

| MEASUREMENT RESULTS                                | 131 |

| 5.3.5.1. STABILITY                                 | 131 |

| 5.3.5.2. SCATTERING PARAMETERS                     |     |

| 5.3.5.3. MAXIMUM OUTPUT POWER       |     |

|-------------------------------------|-----|

| 5.3.5.4. INTERMODULATION DISTORTION |     |

| 5.3.5.5. EFFICIENCY                 | 134 |

| 5.3.5.6. Pout vs. Pin CURVES        | 135 |

| 5.4. SUMMARY                        | 137 |

| 6. CONCLUSION                       | 139 |

| REFERENCES                          | R1  |

| APPENDIX HARMONIC BALANCE METHOD    | A1  |

# LIST OF TABLES

| Table 2.1: Amplitudes of various harmonics in the output2                   | 2 |

|-----------------------------------------------------------------------------|---|

| Table 3.1: Features of LDMOS transistors                                    | 1 |

| Table 3.2: Features of different transistor technologies                    | 2 |

| Table 3.3: Advantages and disadvantages of GaAs MESFET transistor           |   |

| technology3                                                                 | 6 |

| Table 3.4: Advantages and disadvantages of GaAs PHEMT transistor            |   |

| technology3                                                                 | 7 |

| Table 3.5: Advantages and disadvantages of GaAs MHEMT transistor            |   |

| technology3                                                                 | 8 |

| Table 3.6: Advantages and disadvantages of GaAs HBT transistor              |   |

| technology3                                                                 | 9 |

| Table 3.7: Advantages and disadvantages of InP HEMT transistor              |   |

| technology4                                                                 | 0 |

| Table 3.8: Advantages and disadvantages of SiGe HBT transistor              |   |

| technology4                                                                 | 4 |

| Table 3.9: Advantages and disadvantages of GaN HEMT transistor              |   |

| technology4                                                                 | 6 |

| Table 4.1: Comparison of the PCB materials4                                 | 8 |

| Table 4.2: Comparison of IMD result between simulation and measurement for  |   |

| driver stage configuration                                                  | 4 |

| Table 5.1: Effects of driver distortion upon overall distortion             | 5 |

| Table 5.2: The result of maximum output power in comparison between before  |   |

| and after optimization of output matching network12                         | 2 |

| Table 5.3: Comparison of IMD results between simulation and measurement for |   |

| multi stage configuration13                                                 | 3 |

# LIST OF FIGURES

| Figure 2.1: A simple load line for class-A application                                  | 3  |

|-----------------------------------------------------------------------------------------|----|

| Figure 2.2: Stability of two port network                                               | 5  |

| Figure 2.3: Block diagram of an amplifier circuit                                       | 8  |

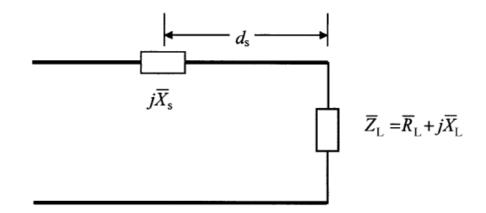

| Figure 2.4: Transmission line with a shunt matching element                             | 9  |

| Figure 2.5: Transmission line with a matching element connected in series               | 11 |

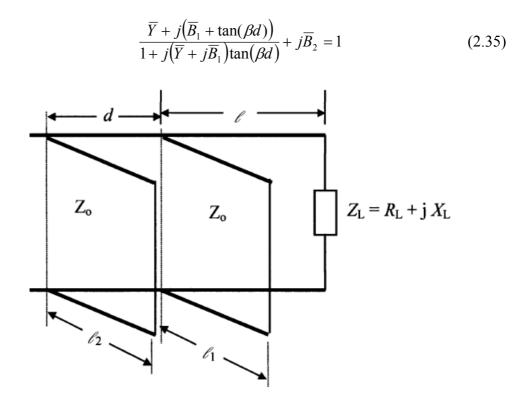

| Figure 2.6: Double-stub matching network                                                | 14 |

| Figure 2.7: Modeling of device output impedance with (a) linear resistance, (b)         |    |

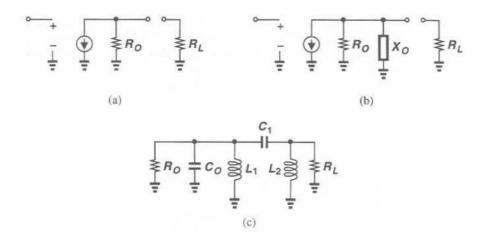

| linear resistance and reactance, (c) simple matching network for (b)                    | 17 |

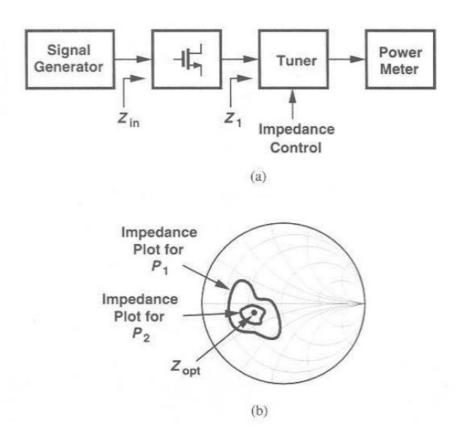

| Figure 2.8: (a) Load-pull test, (b) power contours on a Smith chart                     | 18 |

| Figure 2.9: Nonlinear circuit with input signal $v_i$ that produces $v_o$ at its output | 20 |

| Figure 2.10: Gain characteristics of an amplifier                                       | 22 |

| Figure 2.11: Flow chart of the power amplifier design process                           | 24 |

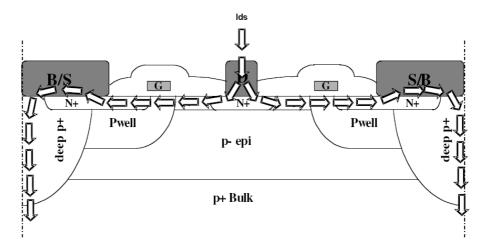

| Figure 3.1: Cross section of an LDMOS transistor                                        | 29 |

| Figure 3.2: Current path in an LDMOS transistor ( $V_{GS} > V_{th}$ )                   | 29 |

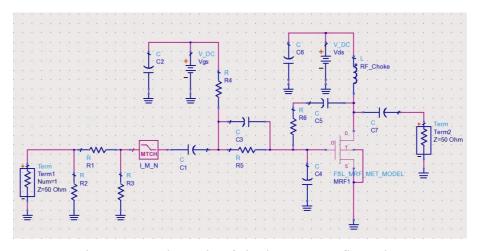

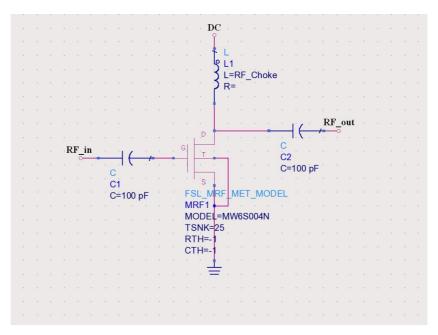

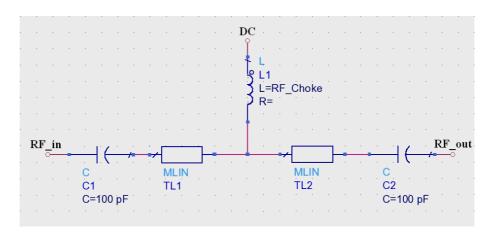

| Figure 4.1: Schematic of single stage configuration                                     | 49 |

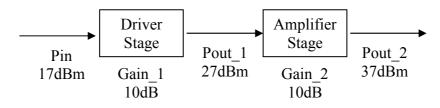

| Figure 4.2: General configuration of two stage power amplifier                          | 50 |

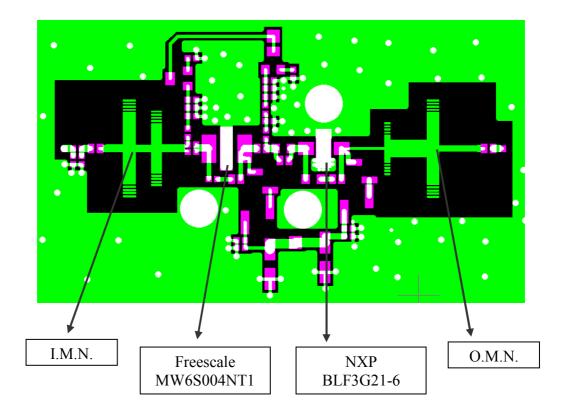

| Figure 4.3: Layout of the overall system on PCB                                         | 51 |

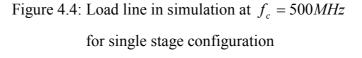

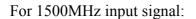

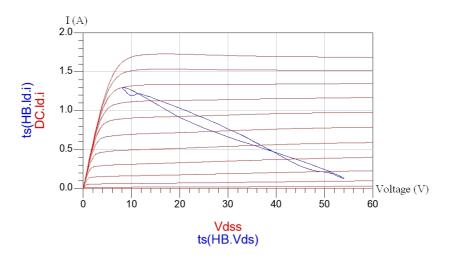

| Figure 4.4: Load line in simulation at $f_c = 500 MHz$ for single stage                 |    |

| configuration                                                                           | 54 |

| Figure 4.5: Load line in simulation at $f_c = 1000MHz$ for single stage                 |    |

| configuration                                                                           | 55 |

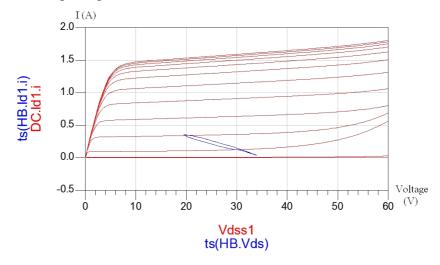

| Figure 4.6: Load line in simulation at $f_c = 1500 MHz$ for single stage                |    |

| configuration                                                                           | 55 |

|                                                                                         |    |

| $r_{s}$                                                                              |    |

|--------------------------------------------------------------------------------------|----|

| configuration                                                                        | 56 |

| Figure 4.8: Basic DC Biasing Network                                                 | 57 |

| Figure 4.9: The position of RF-choke on RF transmission line                         | 57 |

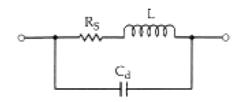

| Figure 4.10: Distributed capacitance and series resistance in an inductor            | 58 |

| Figure 4.11: Inductor equivalent circuit                                             | 59 |

| Figure 4.12: Impedance characteristic vs. frequency for a practical and an ideal     |    |

| inductor                                                                             | 59 |

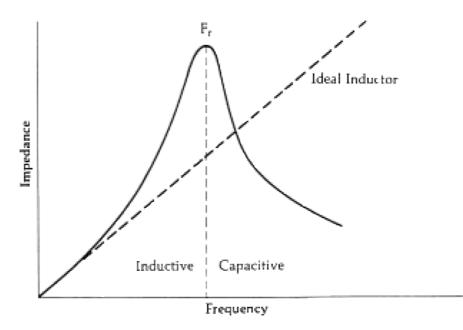

| Figure 4.13: Simulation schematic of two series connected inductors for              |    |

| designing of RF-Choke                                                                | 61 |

| Figure 4.14: Simulation result of series connected Mini Spring Air Core              |    |

| Inductors A05T (18.5 nH) and A03T (8 nH)                                             | 61 |

| Figure 4.15: Measurement S21 result of series connected Mini Spring Air Core         |    |

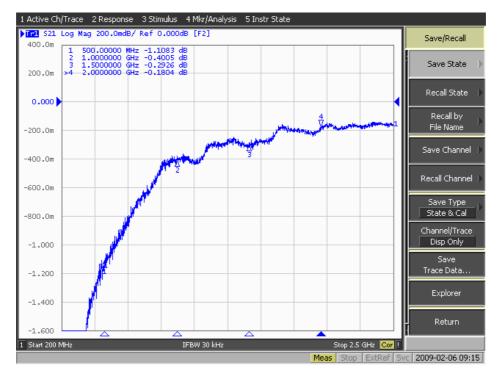

| Inductors A05T (18.5 nH) and A03T (8 nH)                                             | 62 |

| Figure 4.16: Measurement S11 result of series connected Mini Spring Air Core         |    |

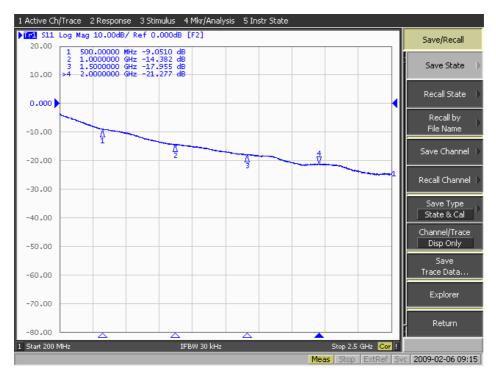

| Inductors A05T (18.5 nH) and A03T (8 nH)                                             | 63 |

| Figure 4.17: Measurement S21 result of series connected Midi Spring Air Core         |    |

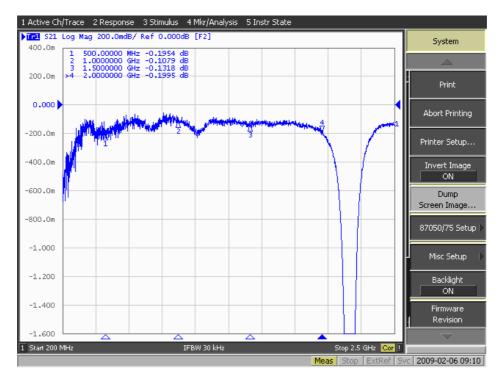

| Inductors of 22nH and Mini Spring Air Core Inductors of                              |    |

| A03T (8nH)                                                                           | 64 |

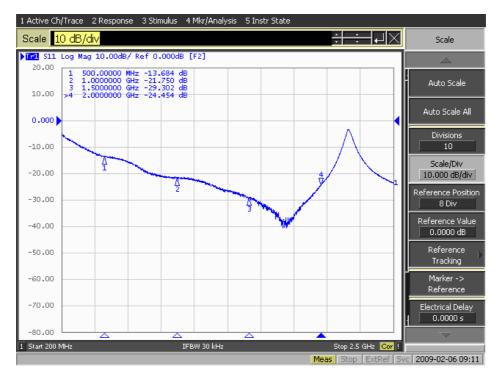

| Figure 4.18: Measurement S11 result of series connected Midi Spring Air Core         |    |

| Inductors of 22nH and Mini Spring Air Core Inductors of                              |    |

| A03T (8 nH)                                                                          | 65 |

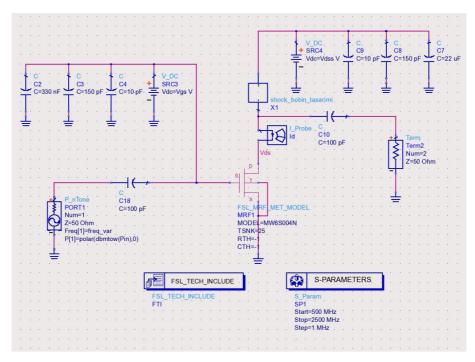

| Figure 4.19: Simulation schematic for verifying the model of MW6S004NT1              |    |

| transistor                                                                           | 66 |

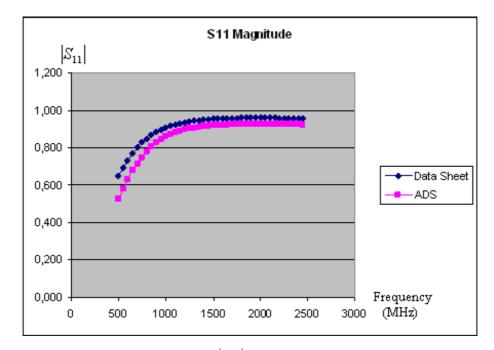

| Figure 4.20: Comparison result of $ S_{11} $ on verified MW6S004NT1 ADS model        | 67 |

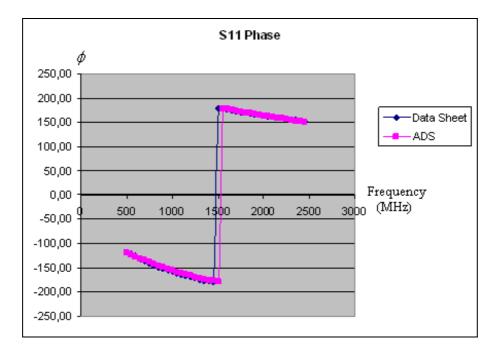

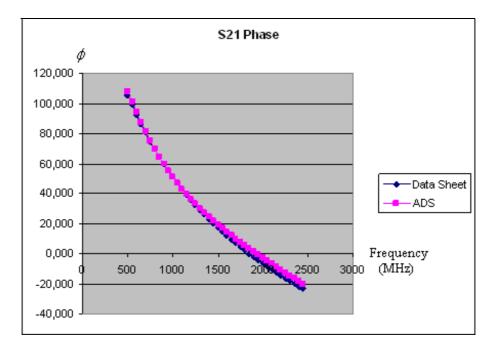

| Figure 4.21: Comparison result of $\angle S_{11}$ on verified MW6S004NT1 ADS model.  | 68 |

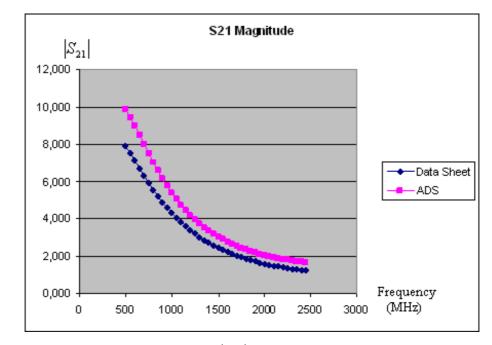

| Figure 4.22: Comparison result of $ S_{21} $ on verified MW6S004NT1 ADS model        | 68 |

| Figure 4.23: Comparison result of $\angle S_{21}$ on verified MW6S004NT1 ADS model . | 69 |

## Figure 4.7: Load line in simulation at $f_c = 2000 MHz$ for single stage

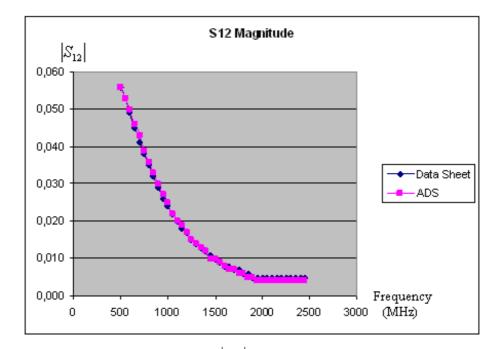

| Figure 4.24: Comparison result of $ S_{12} $ on verified MW6S004NT1 ADS model69         |

|-----------------------------------------------------------------------------------------|

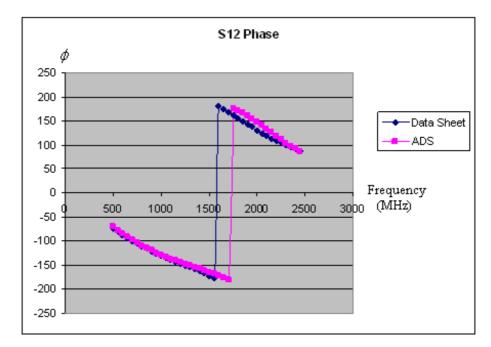

| Figure 4.25: Comparison result of $\angle S_{12}$ on verified MW6S004NT1 ADS model 70   |

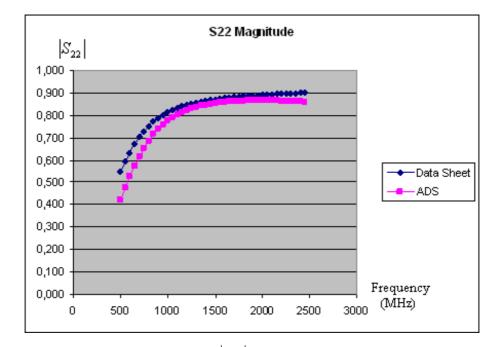

| Figure 4.26: Comparison result of $ S_{22} $ on verified MW6S004NT1 ADS model 70        |

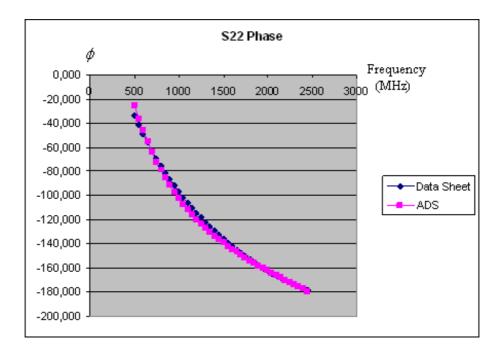

| Figure 4.27: Comparison result of $\angle S_{22}$ on verified MW6S004NT1 ADS model 71   |

| Figure 4.28: Stability analysis that show the optimized components to obtain            |

| unconditionally stable case for driver stage configuration                              |

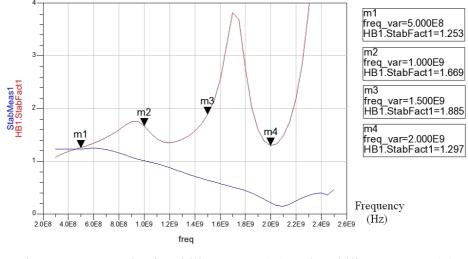

| Figure 4.29: Graph of Stability Factor (K) and Stability Measure (B)                    |

| for driver stage74                                                                      |

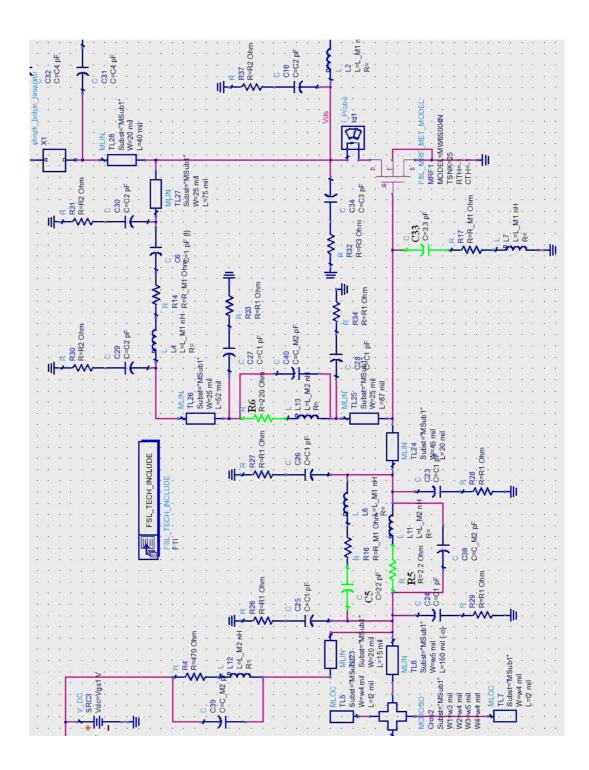

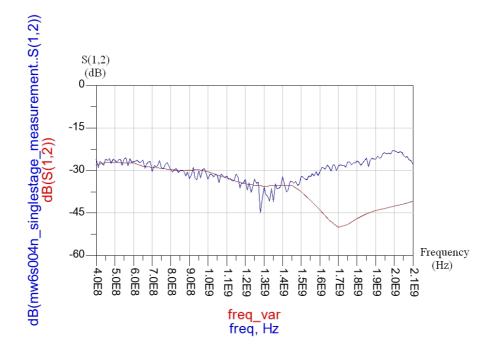

| Figure 4.30: Complete topology in general75                                             |

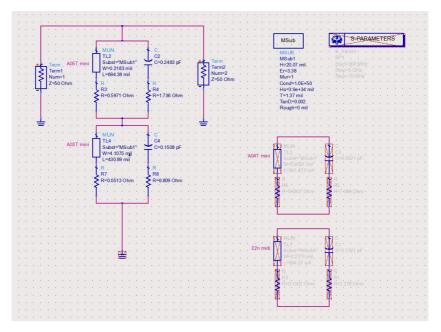

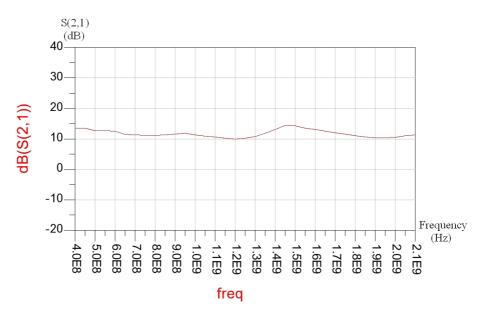

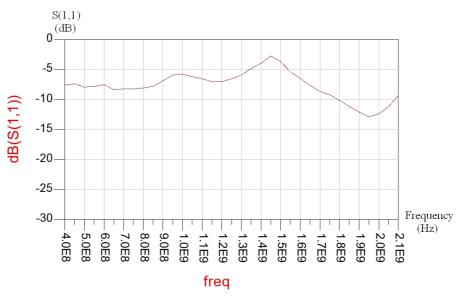

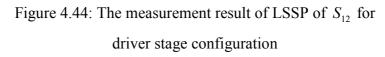

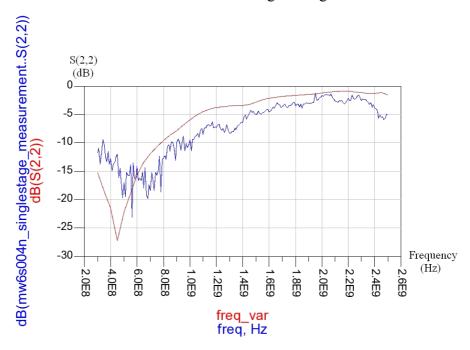

| Figure 4.31: The simulation result of LSSP of $S_{21}$ for driver stage configuration76 |

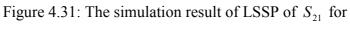

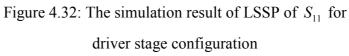

| Figure 4.32: The simulation result of LSSP of $S_{11}$ for driver stage configuration76 |

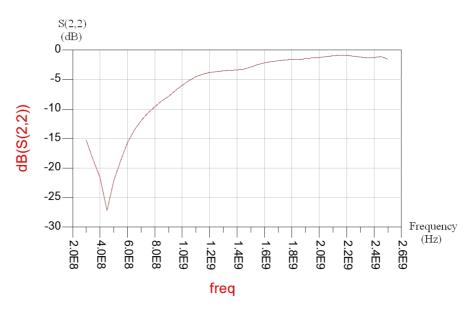

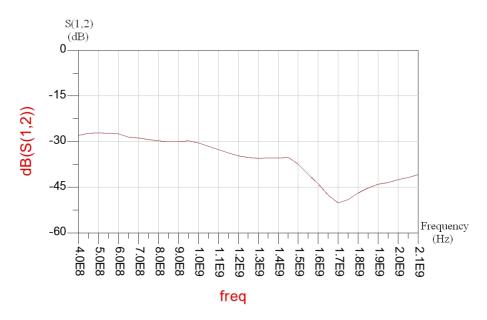

| Figure 4.33: The simulation result of LSSP of $S_{22}$ for driver stage configuration77 |

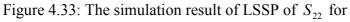

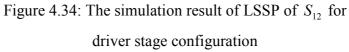

| Figure 4.34: The simulation result of LSSP of $S_{12}$ for driver stage configuration77 |

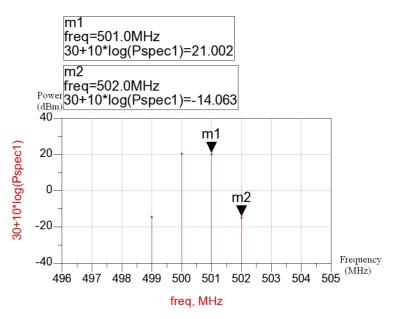

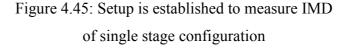

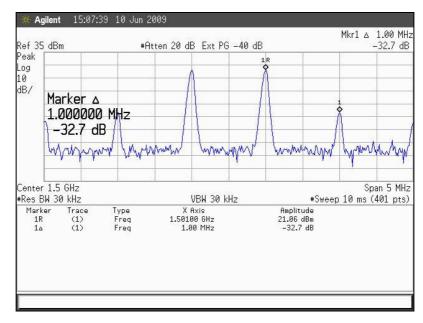

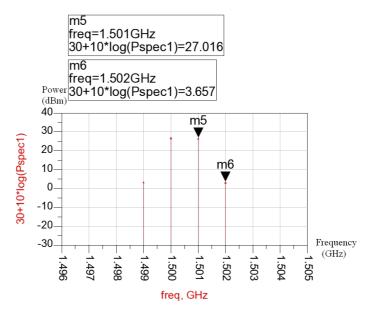

| Figure 4.35: The simulation result of IMD at 500MHz for driver stage                    |

| configuration78                                                                         |

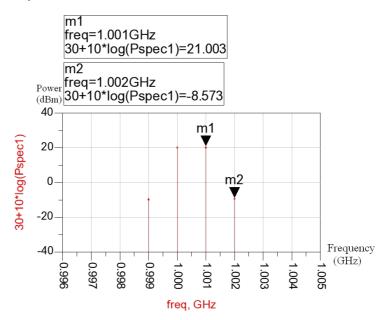

| Figure 4.36: The simulation result of IMD at 1000MHz for driver stage                   |

| configuration79                                                                         |

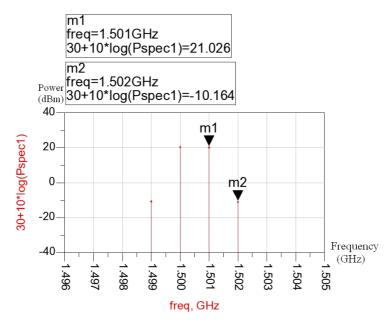

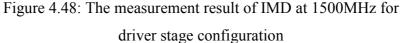

| Figure 4.37: The simulation result of IMD at 1500MHz for driver stage                   |

| configuration79                                                                         |

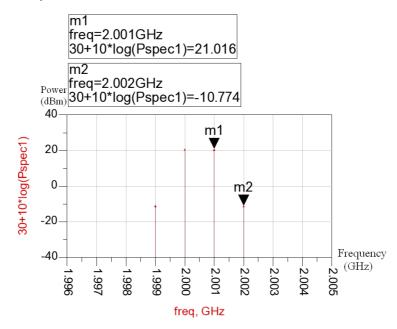

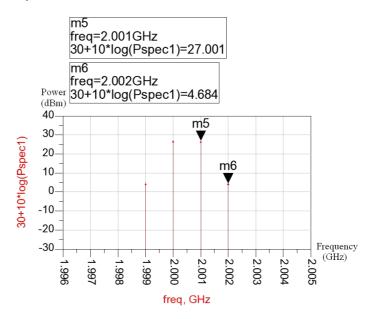

| Figure 4.38: The simulation result of IMD at 2000MHz for driver stage                   |

| configuration80                                                                         |

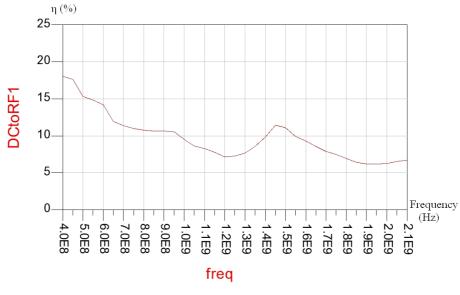

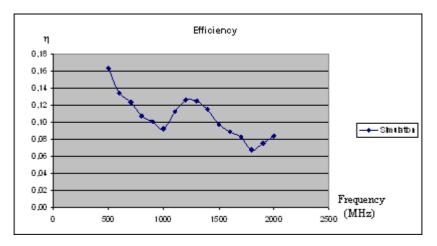

| Figure 4.39: The simulation result of Efficiency for driver stage configuration81       |

| Figure 4.40: The simulation result of 1dB Compression Point for driver stage            |

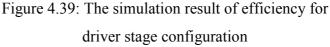

| configuration82                                                                         |

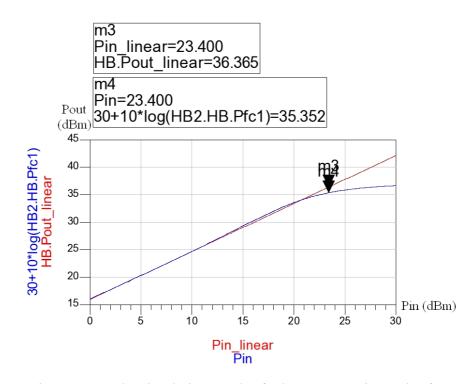

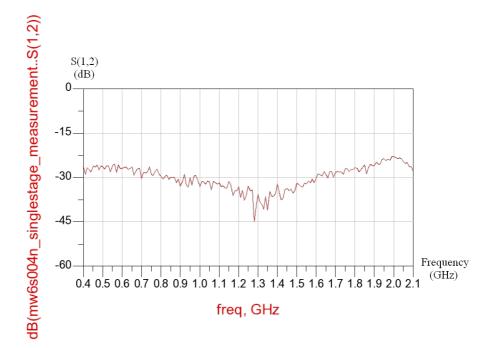

| Figure 4.41: The measurement result of LSSP of $S_{21}$ for driver stage                |

| configuration                                                                           |

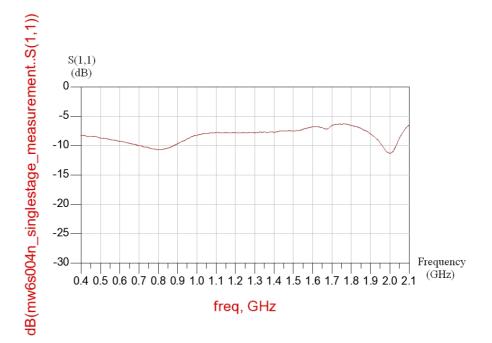

| Figure 4.42: The measurement result of LSSP of $S_{11}$ for driver stage                |

| configuration                                                                           |

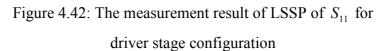

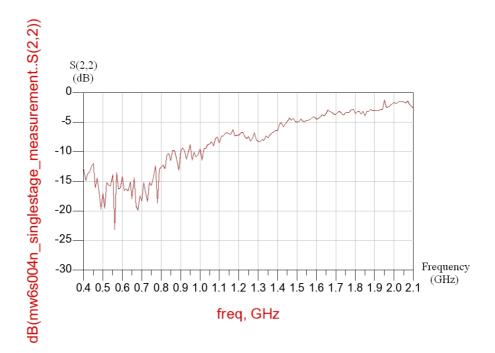

|                                                                                         |

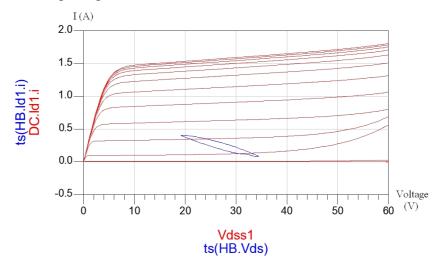

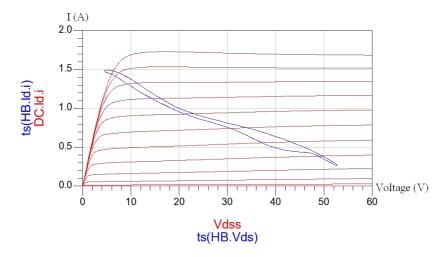

| Figure 5.4: Load line in simulation at $f_c = 1500MHz$ for multi stage                  |

|-----------------------------------------------------------------------------------------|

| configuration103                                                                        |

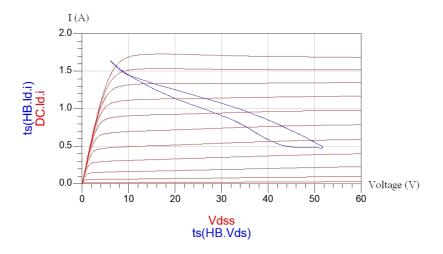

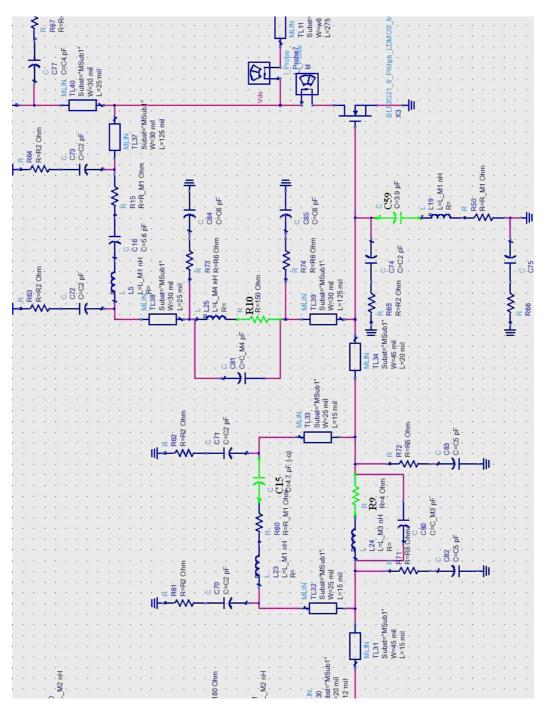

| Figure 5.5: Load line in simulation at $fc = 2000MHz$ for multi stage                   |

| configuration103                                                                        |

| Figure 5.6: Stability analysis that show the optimized components to obtain             |

| unconditionally stable case for last stage configuration                                |

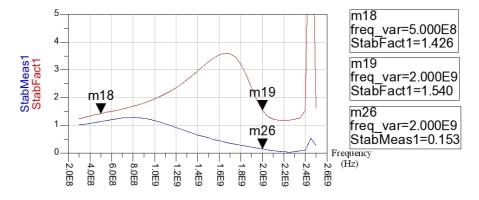

| Figure 5.7: Graphs of Stability Factor (K) and Stability Measure (B) for                |

| last stage                                                                              |

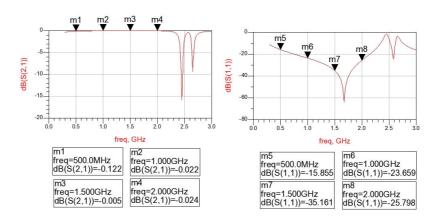

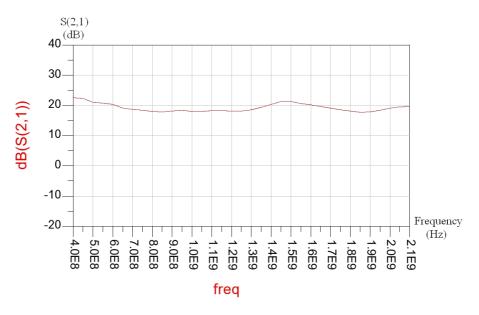

| Figure 5.8: The simulation result of LSSP of $S_{21}$ for multi stage configuration108  |

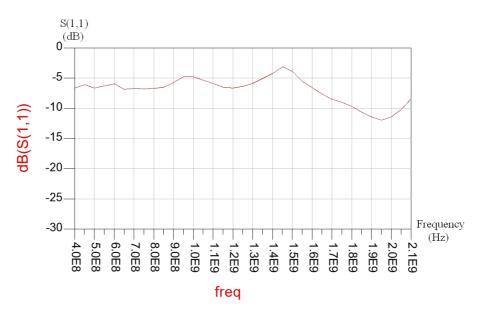

| Figure 5.9: The simulation result of LSSP of $S_{11}$ for multi stage configuration108  |

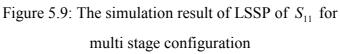

| Figure 5.10: The simulation result of LSSP of $S_{22}$ for multi stage configuration109 |

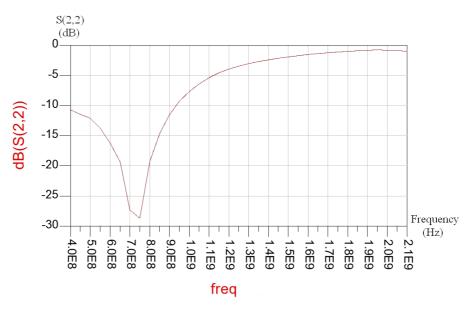

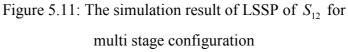

| Figure 5.11: The simulation result of LSSP of $S_{12}$ for multi stage configuration109 |

| Figure 5.12: The simulation result of Maximum Output Power for multi stage              |

| configuration111                                                                        |

| Figure 5.13: The simulation result of IMD at 500MHz for multi stage                     |

| configuration112                                                                        |

| Figure 5.14: The simulation result of IMD at 1000MHz for multi stage                    |

| configuration                                                                           |

| Figure 5.15: The simulation result of IMD at 1500MHz for multi stage                    |

| configuration                                                                           |

| Figure 5.16: The simulation result of IMD at 2000MHz for multi stage                    |

| configuration114                                                                        |

| Figure 5.17: The simulation result of Efficiency for multi stage configuration116       |

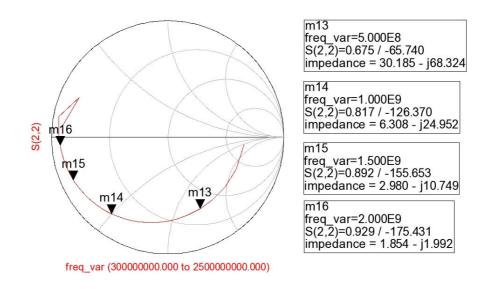

| Figure 5.18: Output impedance of BLF3G21-6 at broadband                                 |

| Figure 5.19: The simulation result of 1dB Compression Point for multi stage             |

| configuration118                                                                        |

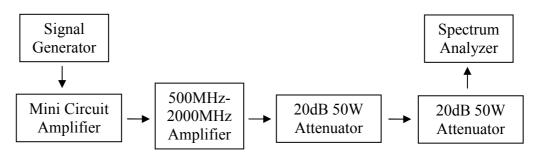

| Figure 5.20: Setup is established to measure large signal s-parameter of $S_{21}$       |

| for multi stage configuration119                                                        |

|                                                                                         |

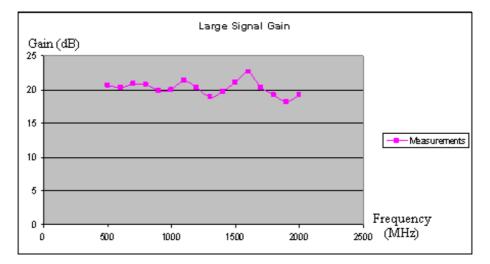

| Figure 5.21: | The measurement result of LSSP of $S_{21}$ for multi stage             |     |

|--------------|------------------------------------------------------------------------|-----|

|              | configuration                                                          | 120 |

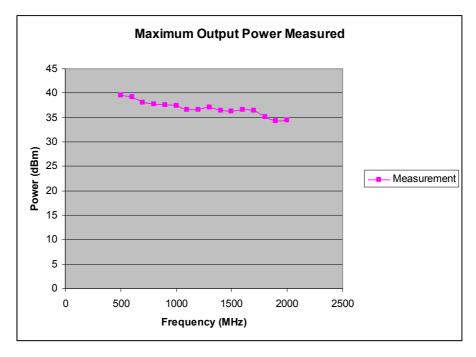

| Figure 5.22: | The measurement result of maximum output power taken from              |     |

|              | the complete amplifier system                                          | 121 |

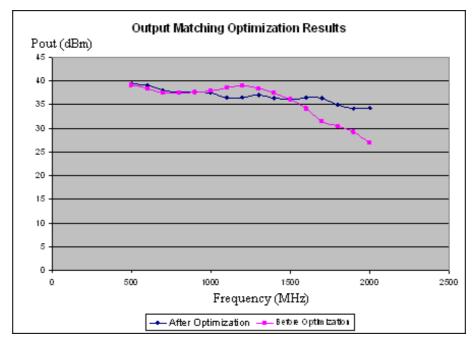

| Figure 5.23: | The result of maximum output power in comparison between               |     |

|              | before and after optimization of output matching network               | 123 |

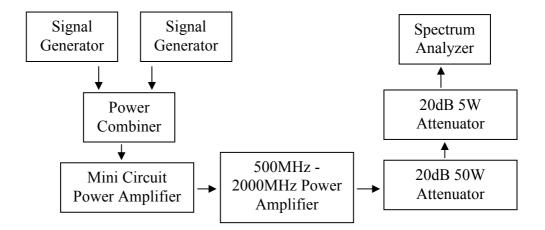

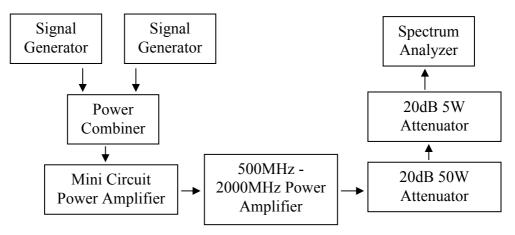

| Figure 5.24: | Setup is established to measure IMD of multi stage configuration       | 124 |

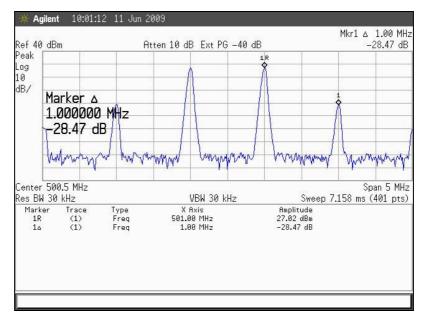

| Figure 5.25: | The measurement result of IMD at 500MHz for multi stage                |     |

|              | configuration                                                          | 125 |

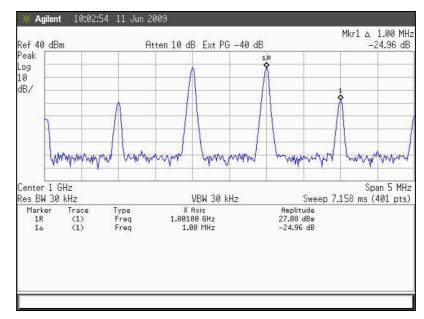

| Figure 5.26: | The measurement result of IMD at 1000MHz for multi stage               |     |

|              | configuration                                                          | 125 |

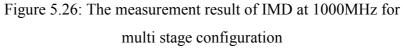

| Figure 5.27: | The measurement result of IMD at 1500MHz for multi stage               |     |

|              | configuration                                                          | 126 |

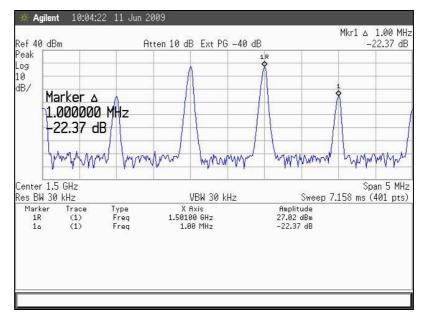

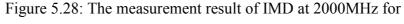

| Figure 5.28: | The measurement result of IMD at 2000MHz for multi stage               |     |

|              | configuration                                                          | 126 |

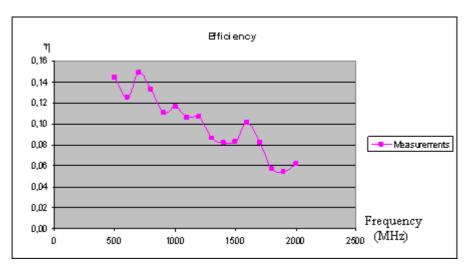

| Figure 5.29: | The measurement result of Efficiency for multi stage configuration     | 127 |

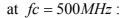

| Figure 5.30: | The measurement result of $P_{out}$ vs. $P_{in}$ curves at 500MHz for  |     |

|              | multi stage configuration                                              | 128 |

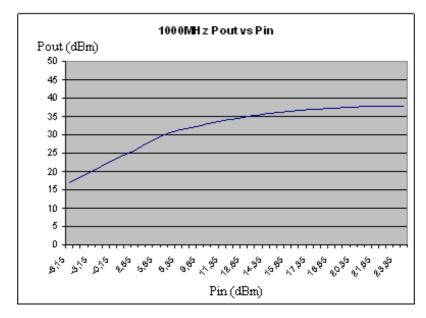

| Figure 5.31: | The measurement result of $P_{out}$ vs. $P_{in}$ curves at 1000MHz for |     |

|              | multi stage configuration                                              | 129 |

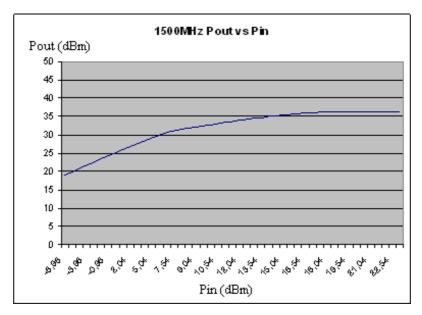

| Figure 5.32: | The measurement result of $P_{out}$ vs. $P_{in}$ curves at 1500MHz for |     |

|              | multi stage configuration                                              | 129 |

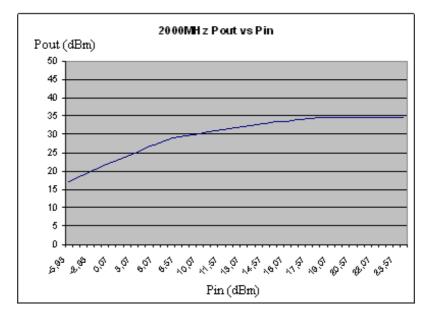

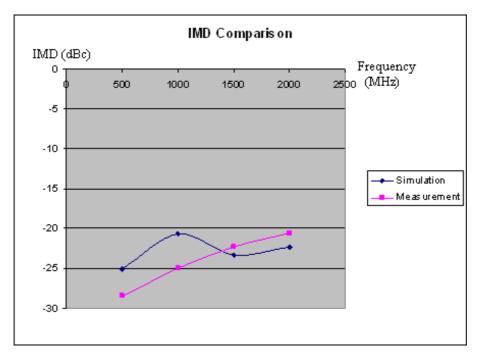

| Figure 5.33: | The measurement result of $P_{out}$ vs. $P_{in}$ curves at 2000MHz for |     |

|              | multi stage configuration                                              | 130 |

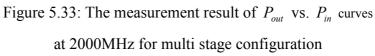

| Figure 5.34: | Comparison of LSSP result of $S_{21}$ between simulation and           |     |

|              | measurement for multi stage configuration                              | 131 |

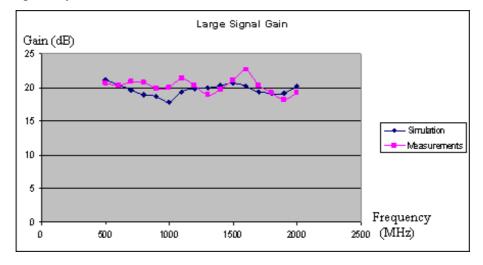

| Figure 5.35: | Comparison of maximum output power between simulation and              |     |

|              | measurement for multi stage configuration                              | 132 |

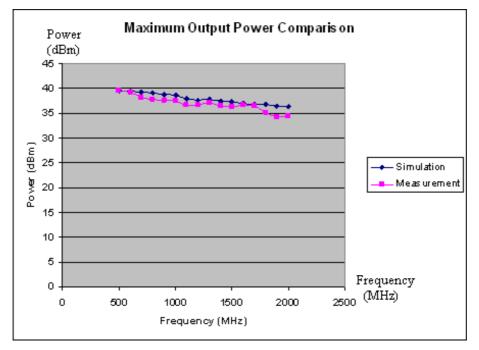

| Figure 5.36: Comparison of IMD results between simulation and measurement        |     |

|----------------------------------------------------------------------------------|-----|

| for multi stage configuration                                                    | 133 |

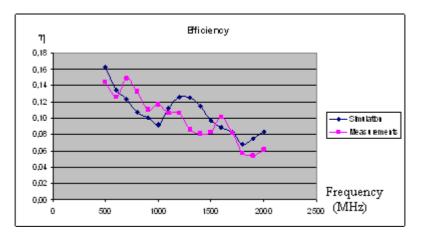

| Figure 5.37: Comparison of efficiency results between simulation and             |     |

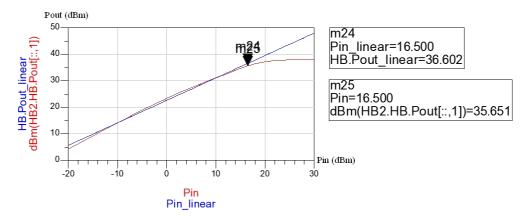

| measurement for multi stage configuration                                        | 134 |

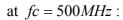

| Figure 5.38: Comparison of $P_{out}$ vs. $P_{in}$ results between simulation and |     |

| measurement at 500MHz for multi stage configuration                              | 135 |

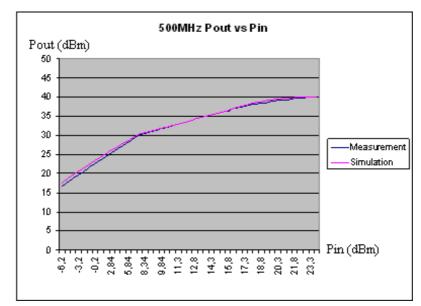

| Figure 5.39: Comparison of $P_{out}$ vs. $P_{in}$ results between simulation and |     |

| measurement at 1000MHz for multi stage configuration                             | 136 |

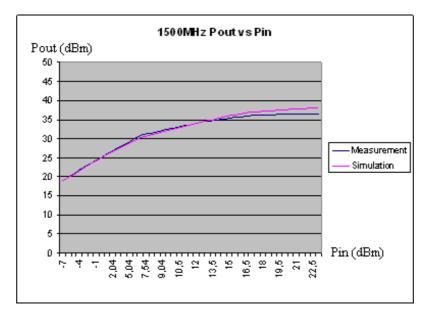

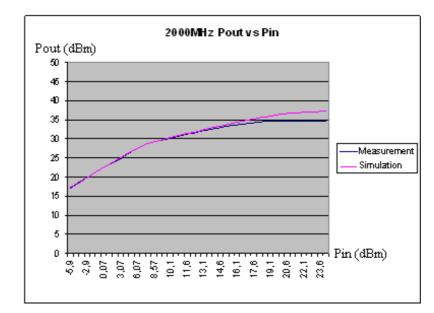

| Figure 5.40: Comparison of $P_{out}$ vs. $P_{in}$ results between simulation and |     |

| measurement at 1500MHz for multi stage configuration                             | 136 |

| Figure 5.41: Comparison of $P_{out}$ vs. $P_{in}$ results between simulation and |     |

| measurement at 2000MHz for multi stage configuration                             | 137 |

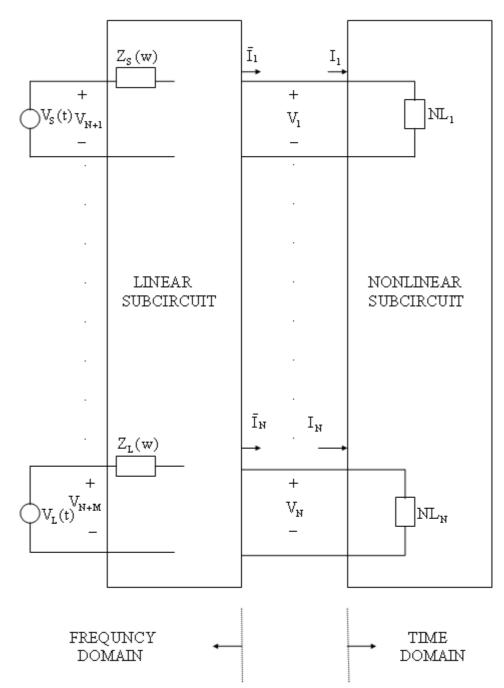

| Figure 7.1: Partitioning of circuit into linear and nonlinear subcircuit         | A3  |

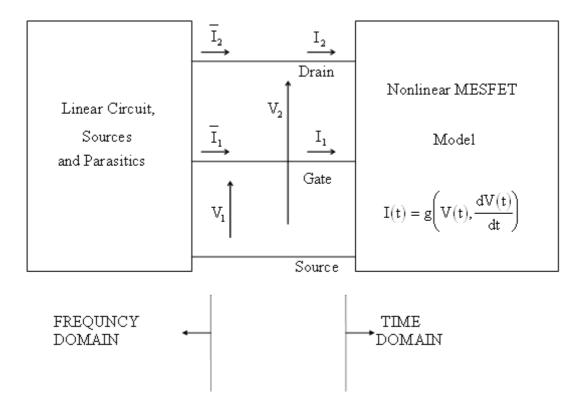

| Figure 7.2: Partitioning of a MESFET circuit to subcircuits.                     | A5  |

|                                                                                  |     |

## **CHAPTER I**

### **INTRODUCTION**

This thesis presents design methods of two stage 5W broadband amplifier covering the frequency range from 500MHz to 2GHz. Power amplifier design is explained theoretically in next chapter. In third chapter, brief information of transistor technologies is given and comparable tables and charts are showed.

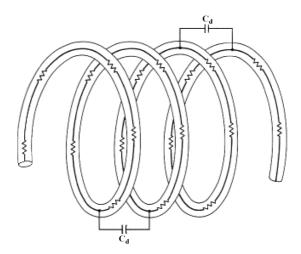

The design features are tried to obtain in two stage power amplifier configuration. In chapter four, single stage design process is explained. Si LDMOS is used in driver and also in last stage. Large signal models are used for the LDMOS devices. PCB materials are searched and the most suitable one (Rogers RO4003C) is selected. A broadband choke structure is developed to obtain high dc isolation and low RF loss over the full bandwidth. In chapter five, multi stage (complete system) design process is explained. Broadband input and output matching networks and shunt feedback topology are introduced to fulfill the bandwidth requirements.

Typical values of 20dB power gain, 37dBm output power, have been achieved in most part of the frequency band of 500MHz-2GHz. All power and linearity results are obtained at the whole frequency band. The design procedure is given in detail and the measurement results are discussed and also compared with simulations.

### **CHAPTER II**

### HIGH POWER RF TRANSISTOR AMPLIFIER DESIGN

It is quite common for new designers to design amplifier with "large signal" analysis. The distinction is quite important because prior to 1985, large-signal analysis was rarely applied to circuits because of its difficulty and the lack of simulation tools. The wealth of analysis centers around S-parameter analysis and equivalent linear characterization of devices, is so tractable and amenable to application that even today we attempt to apply this body of knowledge to components that are clearly large signal in their operation. S-parameters are based upon matrix algebra and the linear addition of incident and reflected voltages. By definition, therefore, they are a linear technique for describing the device. The device being described is assumed invariant to the magnitude (or phase) of the incident and reflected voltages. The attempt to apply them to a device that clearly does not fall into this category is known as quasi-linear analysis. It is needed to be clear about what does it mean by a nonlinear circuit and its impact on component operation [1].

### 2.1. LOAD LINE ANALYSIS

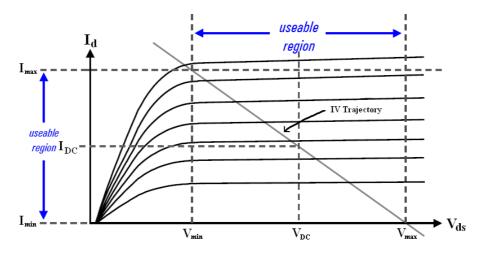

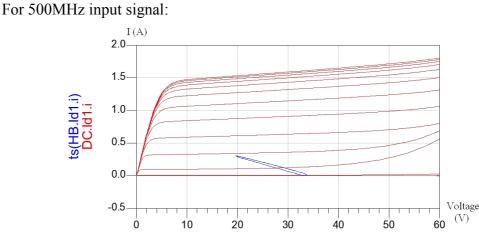

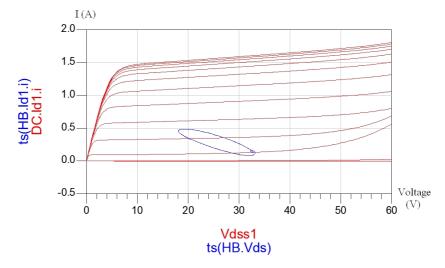

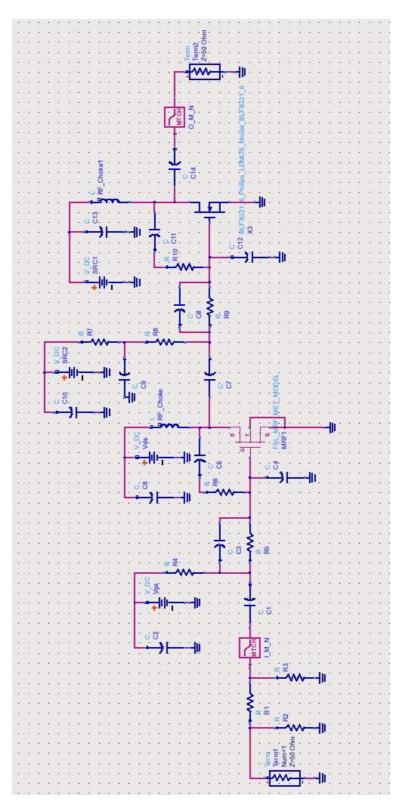

A load line is a technique for finding the optimum impedance to present to the output stage of the power amplifier. If we look at the I-V curves for a FET, we see that there is a useable region for both drain current and drain-to-source voltage.

To keep the output voltage within the linear region of the FET, we avoid the steepsloped areas of the I - V curves [2].

Figure 2.1: A simple load line for class-A application

As seen from the above figure, useable regions for  $V_{ds}$  and  $I_d$  are needed to be used for linear operation. It is important to put a transistor's load line in these regions, because of reducing non-linear effects. Following formulas show what output impedance should be to obtain optimum load line swing for class-A application.

$$V_{RMS} = \frac{V_{\text{max}} - V_{\text{min}}}{2\sqrt{2}} \tag{2.1}$$

$$I_{RMS} = \frac{I_{\max} - I_{\min}}{2\sqrt{2}}$$

(2.2)

then,

$$P_{LOAD} = V_{RMS} I_{RMS} \tag{2.3}$$

s0,

$$P_{LOAD} = \frac{(V_{\max} - V_{\min})(I_{\max} - I_{\min})}{8}$$

(2.4)

where  $P_{LOAD}$  is known according to the specification of design.  $V_{max}$  and  $V_{min}$  can be found from DC analysis of a transistor.  $I_{min}$  is approximately 0 for RF power transistors. So,  $R_L$  can be found

$$R_{L} = \frac{(V_{\max} - V_{\min})}{(I_{\max} - I_{\min})}$$

(2.5)

from the above formula [3].

According to the figure these relations can be said.

- Slope of a load line is related with the value of  $R_L$ ,

- position of a load line in y-axis is related with  $V_{GS}$  (biasing point),

- length of a load line is related with  $P_{in}$  (input power).

So, load line of a transistor is adjusted according to the above relations.

### 2.2. STABILITY CONSIDERATIONS

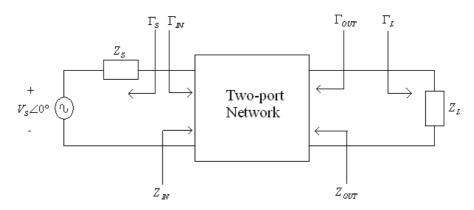

The stability of an amplifier, or its resistance to oscillate, is a very important consideration in a design and can be determined from the S parameters, the matching networks, and the terminations. In a two-port network, oscillations are possible when either the input or output port presents a negative resistance. This occurs when  $|\Gamma_{IN}| > 1$  or  $|\Gamma_{OUT}| > 1$ , which for a unilateral device occurs when  $|S_{11}| > 1$  or  $|S_{22}| > 1$ .

The two-port network shown in Figure 2.2 is said to be unconditionally stable at a given frequency if the real parts of  $Z_{IN}$  and  $Z_{OUT}$  are greater than zero for all passive load and source impedances. If the two-port is not unconditionally stable, it

is potentially unstable. That is, some passive load and source terminations can produce input and output impedances having a negative real part.

Figure 2.2: Stability of two port network

In terms of reflection coefficients, the conditions for unconditional stability at a given frequency are

$$\left|\Gamma_{s}\right| < 1 \tag{2.6}$$

$$\left| \Gamma_L \right| < 1 \tag{2.7}$$

$$\left|\Gamma_{IN}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}\right| < 1$$

(2.8)

and

$$\left|\Gamma_{OUT}\right| = \left|S_{22} + \frac{S_{12}S_{21}\Gamma_{S}}{1 - S_{11}\Gamma_{S}}\right| < 1$$

(2.9)

where, of course, all coefficients are normalized to the same characteristic impedance  $Z_0$ .

The solutions of (2.6) to (2.7) give the required conditions for the two-port network to be unconditionally stable [4].

Condition (2.8) can be rearranged as follows:

$$\left| S_{11} + \frac{S_{22}S_{12}S_{21}\Gamma_L + (S_{12}S_{21} - S_{12}S_{21})}{S_{22}(1 - S_{22}\Gamma_L)} \right| < 1$$

(2.10)

or,

$$\left| \frac{1}{S_{22}} \left( \Delta + \frac{S_{12} S_{21}}{1 - S_{22} \Gamma_L} \right) \right| < 1$$

(2.11)

where,

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{2.12}$$

after some manipulations,

$$1 - \left|S_{22}\right|^2 - \left|S_{12}S_{21}\right| > 0 \tag{2.13}$$

similarly, stability condition (2.9) will be satisfied if

$$1 - \left|S_{11}\right|^2 - \left|S_{12}S_{21}\right| > 0 \tag{2.14}$$

adding (2.13) and (2.14), we get

$$2 - |S_{11}|^2 - |S_{22}|^2 - 2|S_{12}S_{21}| > 0$$

(2.15)

or,

$$1 - \frac{1}{2} \left( \left| S_{11} \right|^2 - \left| S_{22} \right|^2 \right) > 2 \left| S_{12} S_{21} \right|$$

(2.16)

from (2.12) and (2.16), we have

$$\left|\Delta\right| < \left|S_{11}S_{22}\right| + \left|S_{12}S_{21}\right| < \left|S_{11}S_{22}\right| + 1 - \frac{1}{2}\left(\left|S_{11}\right|^2 - \left|S_{22}\right|^2\right)$$

(2.17)

or,

$$\Delta | < 1 - \frac{1}{2} (|S_{11}| - |S_{22}|)^2 \Longrightarrow |\Delta| < 1$$

(2.18)

6

on the other hand,

$$1 - |S_{11}|^2 - |S_{22}|^2 - 2|S_{12}S_{21}| + |\Delta|^2 > 0$$

(2.19)

or,

$$1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2 > 2|S_{12}S_{21}|$$

(2.20)

or,

$$\frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} > 1$$

(2.21)

therefore,

$$k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} > 1$$

(2.22)

If S-parameters of a transistor satisfy conditions (2.18) and (2.22) then it is stable for any passive load and generator impedance. In other words, this transistor is *unconditionally stable*. On the other hand, it may be conditionally stable (stable for limited values of load or source impedance) if one or both of these conditions are violated. It means that the transistor can provide stable operation for a restricted range of  $\Gamma_s$  and  $\Gamma_L$ .

#### 2.3. IMPEDANCE MATCHING NETWORKS

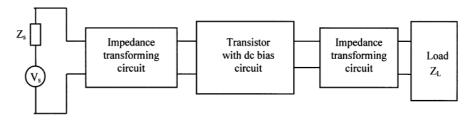

One of the most critical requirements in the design of high-frequency electronic circuits is that the maximum possible signal energy is transferred at each point. In other words, the signal should propagate in a forward direction with a negligible echo (ideally, zero). Echo signal not only reduces the power available but also deteriorates the signal quality due to the presence of multiple reflections. Impedance can be transformed to a new value by adjusting the turn ratio of a transformer that couples it with the circuit. However, it has several limitations. In

this section a few techniques to design other impedance transforming networks are presented. These circuits include transmission line stubs, and resistive and reactive networks. Further, the techniques introduced are needed in active circuit design at RF and microwave frequencies.

As shown in Figure 2.3, impedance matching networks are employed at the input and the output of an amplifier circuit. These networks may also be needed to perform some other tasks, such as filtering the signal and blocking or passing the dc bias voltages. This section begins with impedance matching techniques that use a single reactive element or stub connected in series or in shunt. Theoretical principles

Figure 2.3: Block diagram of an amplifier circuit

behind the technique are explained.

### Single Reactive Element or Stub Matching

When a lossless transmission line is terminated by an impedance  $Z_L$ , the magnitude of the reflection coefficient (and hence, the VSWR) on it remains constant but its phase angle can be anywhere between +180° and -180°. As one moves away from the load, impedance (or the admittance) value changes. This movement is clockwise on the VSWR circle. The real part of the normalized impedance (or the normalized admittance) becomes unity at certain points on the line. Addition of a single reactive element or a transmission line stub at this point can eliminate the echo signal and reduce the VSWR to unity beyond this point. A finite-length transmission line with its other end open or short circuit is called the stub and behaves like a reactive element.

In this section, the procedure for determining the location on a lossless feeding line is discussed where a stub or a reactive element can be connected to eliminate the echo signal. Two different possibilities, a series or a shunt element, are considered.

### A Shunt Stub or Reactive Element

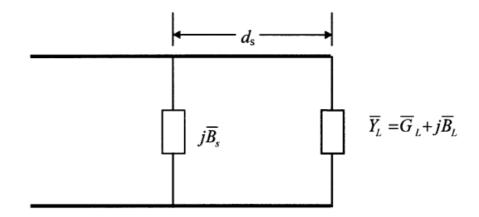

Consider a lossless transmission line of characteristic impedance  $Z_0$  that is terminated by a load admittance  $Y_L$ , as shown in Figure 2.4. Corresponding normalized input admittance at a point  $d_s$  away from the load can be found from as follows:

$$\overline{Y}_{in} = \frac{\overline{Y}_L + j \tan(\beta d_s)}{1 + j \overline{Y}_L \tan(\beta d_s)}$$

(2.23)

Figure 2.4: Transmission line with a shunt matching element

In order to obtain a matched condition at  $d_s$ , the real part of the input admittance must be equal to the characteristic admittance of the line; i.e., the real part of (2.23) must be unity. This requirement is used to determine  $d_s$ . The parallel susceptance  $B_s$  is then connected at  $d_s$  to cancel out the imaginary part of  $Y_{in}$ . Hence,

$$ds = \frac{1}{\beta} \tan^{-1} \left( \frac{\overline{B}_L \pm \sqrt{\overline{B}_L^2 - A(1 - \overline{G}_L)}}{A} \right)$$

(2.24)

where  $A = \overline{G}_L (\overline{G}_L - 1) + {B_L}^2$ .

The imaginary part of the normalized input admittance at  $d_s$  is found as follows.

$$\overline{B}_{in} = \frac{\left\{\overline{B}_{L} + \tan(\beta d_{s})\right\} \times \left\{1 - \overline{B}_{L} \tan(\beta d_{s})\right\} - \overline{G}_{L}^{2} \tan(\beta d_{s})}{\left\{\overline{G}_{L} \tan(\beta d_{s})\right\}^{2} + \left\{1 - \overline{B}_{L} \tan(\beta d_{s})\right\}^{2}}$$

(2.25)

The other requirement to obtain a matched condition is

$$\overline{B}_s = -\overline{B}_{in} \tag{2.26}$$

Hence, shunt inductor is needed at  $d_s$  if the input admittance is found capacitive (i.e.,  $\overline{B}_{in}$  is positive). On the other hand, it will require a capacitor if  $Y_{in}$  is inductive at  $d_s$ . A lossless transmission line section can be used in place of this inductor or capacitor. Length of this transmission line section is determined according to the susceptance needed by (2.26) and the termination (i.e., an open circuit or a short circuit) at its other end. This transmission line section is called a *stub*. If  $\ell_s$  is the stub length that has a short circuit at its other end, then

$$\ell_s = \frac{1}{\beta} \cot^{-1}(-\overline{B}_s) = \frac{1}{\beta} \cot^{-1}(-\overline{B}_{in})$$

(2.27)

On the other hand, if there is an open circuit at the other end of the stub, then

$$\ell_s = \frac{1}{\beta} \tan^{-1}(\overline{B}_s) = \frac{1}{\beta} \tan^{-1}(-\overline{B}_{in})$$

(2.28)

#### A Series Stub or Reactive Element

If a reactive element (or a stub) needs to be connected in series as shown in Figure 2.5, the design procedure can be developed as follows. The normalized input impedance at  $d_s$  is

$$\overline{Z}_{in} = \frac{\overline{Z}_L + j \tan(\beta d_s)}{1 + j\overline{Z}_L \tan(\beta d_s)}$$

(2.29)

Figure 2.5: Transmission line with a matching element connected in series

In order to obtain a matched condition at  $d_s$ , the real part of the input impedance must be equal to the characteristic impedance of the line; i.e., the real part of (2.29) must be unity. This condition is used to determine  $d_s$ . A reactance  $X_s$  is then connected in series at  $d_s$  to cancel out the imaginary part of  $Z_{in}$ . Hence,

$$d_{s} = \frac{1}{\beta} \tan^{-1} \left( \frac{\overline{X}_{L} \pm \sqrt{\overline{X}_{L}^{2} - A_{z} \left(1 - \overline{R}_{L}\right)}}{A_{z}} \right)$$

(2.30)

where  $A_z = \overline{R}_L (\overline{R}_L - 1) + \overline{X}_L^2$ .

The imaginary part of the normalized input impedance at  $d_s$  is found as follows.

$$\overline{X}_{in} = \frac{\left\{\overline{X}_{L} + \tan(\beta d_{s})\right\} \times \left\{1 - \overline{X}_{L} \tan(\beta d_{s})\right\} - \overline{R}_{L}^{2} \tan(\beta d_{s})}{\left\{\overline{R}_{L} \tan(\beta d_{s})\right\}^{2} + \left\{1 - \overline{X}_{L} \tan(\beta d_{s})\right\}^{2}}$$

(2.31)

In order to obtain a matched condition at  $d_s$ , the reactive part  $X_{in}$  must be eliminated by adding an element of opposite nature. Hence,

$$\overline{X}_s = -\overline{X}_{in} \tag{2.32}$$

Therefore, a capacitor will be needed in series if the input impedance is inductive. It will require an inductor if input reactance is capacitive. A transmission line stub can be used instead of an inductor or a capacitor. Length of this stub with an open circuit at its other end can be determined as follows.

$$\ell_s = \frac{1}{\beta} \cot(-\overline{X}_s) = \frac{1}{\beta} \cot(-\overline{X}_{in})$$

(2.33)

However, if the stub has a short circuit at its other end, its length will be a quarterwavelength shorter (or longer, if the resulting number becomes negative) than this value. It can be found as

$$\ell_s = \frac{1}{\beta} \tan(\overline{X}_s) = \frac{1}{\beta} \tan(-\overline{X}_{in})$$

(2.34)

12

Note that the location  $d_s$  and the stub length  $\ell_s$  are periodic in nature in both cases. It means that the matching conditions will also be satisfied at points one-half wavelength apart. However, the shortest possible values of  $d_s$  and  $\ell_s$  are preferred because those provide the matched condition over a broader frequency band [5].

#### **Double Stub Matching**

The matching technique presented in the preceding section requires that a reactive element or stub be placed at a precise distance from the load. This point will shift with load impedance. Sometimes it may not be feasible to match the load using a single reactive element. Another possible technique to match the circuit employs two stubs with fixed separation between them. This device can be inserted at a convenient point before the load. The impedance is matched by adjusting the lengths of the two stubs. Of course, it does not provide a universal solution. Separation between the two stubs limits the range of load impedance.

Let  $\ell_1$  and  $\ell_2$  be the lengths of two stubs, as shown in Figure 2.6. The first stub is located at a distance  $\ell$  from the load,  $Z_L = R + jX$  ohm. Separation between the two stubs is d, and characteristic impedance of every transmission line is  $Z_0$ . In double-stub matching, load impedance  $Z_L$  is transformed to normalized admittance at the location of the first stub. Since the stub is connected in parallel, its normalized susceptance is added to that and then the resulting normalized admittance is transferred to the location of second stub. Matching conditions at this point require that the real part of this normalized admittance be equal to unity while its imaginary part is canceled by a conjugate susceptance of the second stub. Mathematically,

Figure 2.6: Double-stub matching network

where,

$$\overline{Y} = \frac{1+j\overline{Z}_L \tan(\beta\ell)}{\overline{Z}_L + j \tan(\beta\ell)} = \frac{\overline{Y}_L + j \tan(\beta\ell)}{1+j\overline{Y}_L \tan(\beta\ell)} = \overline{G} + j\overline{B}$$

(2.36)

where  $jB_1$  and  $jB_2$  are the susceptance of the first and second stubs, respectively, and  $\beta$  is the propagation constant over the line.

For,

$$\operatorname{Re}\frac{\overline{Y} + j(\overline{B}_{1} + \tan(\beta d))}{1 + j(\overline{Y} + j\overline{B}_{1})\tan(\beta d)} = 1$$

(2.37)

$$\overline{G}^{2} \tan^{2}(\beta d) - \overline{G} \left\{ 1 + \tan^{2}(\beta d) \right\} + \left\{ 1 - \left( \overline{B} + \overline{B}_{1} \right) \tan(\beta d) \right\}^{2} = 0$$

(2.38)

14

Since conductance of the passive network must be a positive quantity, (2.38) requires that a given double stub can be used for matching only if the following condition is satisfied.

$$0 \le \overline{G} \le \csc^2(\beta d) \tag{2.39}$$

Two possible susceptances of the first stub that can match the load are determined by solving (2.38) as follows.

$$\overline{B}_{1} = \cot(\beta d) \left[ 1 - \overline{B} \tan(\beta d) \pm \sqrt{\overline{G} \sec^{2}(\beta d)} - \left\{ \overline{G} \tan(\beta d) \right\}^{2} \right]$$

(2.40)

Normalized susceptance of the second stub is determined from (2.35) as follows:

$$\overline{B}_{2} = \frac{\overline{G}^{2} \tan(\beta d) - \left\{\overline{B} + \overline{B}_{1} + \tan(\beta d)\right\} \times \left\{1 - \left(\overline{B} + \overline{B}_{1}\right)\tan(\beta d)\right\}}{\left\{\overline{G} \tan(\beta d)\right\}^{2} + \left\{1 - \left(\overline{B} + \overline{B}_{1}\right)\tan(\beta d)\right\}^{2}}$$

(2.41)

Once the susceptance of a stub is known, its short-circuit length can be determined easily as follows [6]:

$$\ell_1 = \frac{1}{\beta} \cot^{-1}(-\overline{B}_1) \tag{2.42}$$

and,

$$\ell_{2} = \frac{1}{\beta} \cot^{-1}(-\overline{B}_{2})$$

(2.43)

### 2.4. LARGE SIGNAL IMPEDANCE MATCHING

Power amplifiers usually employ a matching network between the output transistor and the load. In a class-A stage, if the transistor behaved as an ideal current source, the matching network would simply transform the load resistance to a lower value while presenting no reactive components. In practice, however, the output impedance of the active device is finite, exhibits both real and imaginary parts, and varies with the output voltage and current. Thus, a nonlinear complex output impedance must be matched to a linear load. While we assume herein that the load is resistive and constant, in reality the impedance of the antenna may both contain a reactive component and vary with the position of the transceiver with respect to external objects.

Before dealing with the task of nonlinear impedance matching; first, consider a simple case where the transistor is modeled as an ideal current source with a linear resistive output impedance [Figure 2.7(a)]. An apparent contradiction that occurs here is that the maximum power transfer theorem mandates that  $R_L = R_0$ , it is required that  $R_L$  be transformed to a small value, i.e., typically  $R_L << R_0$ . Which choice is logical here? If  $R_L = R_0$ , two problems arise. First, the power delivered to  $R_L$  is equal to that dissipated in  $R_0$ , reducing the peak efficiency of a class-A amplifier from 50% to 25%. In other words, maximum power transfer does not correspond to maximum efficiency. Second, if  $R_L$  is transformed to be as high as  $R_0$ , the output power is quite small, the output power is quite small, unless a high supply voltage is used. For these reasons in typical power amplifiers,  $R_L << R_0$ .

Figure 2.7: Modeling of device output impedance with (a) linear resistance,(b) linear resistance and reactance, (c) simple matching network for (b)

In the next step, suppose, as shown in Figure 2.7(b), the transistor output impedance contains linear real and imaginary parts. Note that since the output transistor is typically several millimeters wide, the magnitude of  $X_0$  at high frequencies is relatively small. The matching network must therefore provide a reactive component to cancel the effect of  $X_0$ . Figure 2.7(c) illustrates a simple example where  $L_1$  cancels  $C_0$ , and  $C_1$  and  $L_2$  transform  $R_L$  while resonating at the fundamental frequency.

Now consider the general case of a nonlinear complex output impedance. A smallsignal approximation of the impedance in the midrange of output voltage can be used to obtain rough values for the matching network components, but modifying these values for maximum large-signal efficiency requires a great deal of trial and error, especially if package parasitics must be taken into account. In practice, a more systematic approach called *"load-pull measurement"* is employed.

In a load-pull test, the output power is measured and plotted as a function of the complex load seen by the transistor. Since a complex load requires two axes, the plot actually appears as constant power contours on a complex impedance plane, for

example, a Smith chart. Figure 2.8(a) shows a conceptual setup for load-pull measurement. A variable, precisely calibrated tuner operates as a matching network, presenting various complex impedances to the transistor according to a control input. With the aid of an automated system, the real and imaginary parts of  $Z_1$  are gradually varied such that the power meter maintains a constant reading [Figure 2.8(b)]. In practice, as  $Z_1$  varies so does  $Z_{in}$ , necessitating the use of a second tuner between the signal generator and the transistor such that the impedance seen by the generator remains constant (and usually equal to  $50\Omega$ ).

Figure 2.8: (a) Load-pull test, (b) power contours on a Smith chart.

If the power delivered to the input is constant, the output power increases as  $Z_1$  approaches its optimum value,  $Z_{opt}$ . This trend is accompanied by a narrower range for  $Z_1$ , resulting in tighter contours and eventually a single impedance value,

$Z_{opt}$ , as the output power reaches its maximum level,  $P_{max}$ . In other words, the load- pull test systematically narrows down the values of  $Z_1$  so as to obtain both the maximum output power and the corresponding load impedance. Note the power contours also indicate the sensitivity of  $P_{out}$  with respect to errors in the choice of  $Z_1$ .

The load-pull technique has been widely used in power amplifier design, although it generally requires a computer-controlled setup with extremely precise and stable tuners. This method, however, suffers from three drawbacks. First, the measured results for one device size cannot be directly applied to a different size. Second, the contours and impedance levels are measured at a single frequency and fail to predict the behavior at other frequencies. Third, since the load-pull algorithm does not necessarily provide peaking at higher harmonics, it cannot predict the efficiency and the output power in the presence of multiharmonic termination. For these reasons, power amplifier design using load pull data still entails some trail and error.

In order to avoid complex test setups, the load-pull method can alternatively be implemented in circuit simulation. Similar to the above procedure, the load impedance is varied in small steps and constant power contours are constructed, eventually providing the value of  $Z_{opt}$ . Here, too, the procedure is lengthy and cumbersome unless the load variation is automated. Furthermore, such a simulation requires precise modeling of transistors, in particular their output impedance, whereas SPICE models do not accurately represent the output impedance of device at high frequencies and under large variations of voltage and current [7].

# 2.5. INTERMODULATION DISTORTION & 1-dB COMPRESSION POINT

The electrical noise of a system determines the minimum signal level that it can detect. On the other hand, the signal will be distorted if its level is too high. This occurs because of the nonlinear characteristics of electrical devices such as diodes, transistors, and so on. In this section, distortion characteristics are analyzed.

Figure 2.9: Nonlinear circuit with input signal  $v_i$  that produces  $v_o$  at its output

Consider the nonlinear system illustrated in Figure 2.9. Assume that its nonlinearity is frequency independent and can be represented by the following power series

$$v_o = k_1 v_i + k_2 v_i^2 + k_3 v_i^3 + \dots$$

(2.44)

For simplicity, we assume that the  $k_i$  are the real and the first three terms of this series are sufficient to represent its output signal. Further, it is assumed that the input signal has two different frequency components that can be expressed as follows:

$$v_i = a\cos(w_1t) + b\cos(w_2t)$$

(2.45)

Therefore, the corresponding output signal can be written as

$$v_o \approx k_1 [a\cos(w_1 t) + b\cos(w_2 t)] + k_2 [a\cos(w_1 t) + b\cos(w_2 t)]^2 + k_3 [a\cos(w_1 t) + b\cos(w_2 t)]^3$$

(2.46)

After simplifying and rearranging it we get

$$v_{o} = k_{1} \left[ a \cos(w_{1}t) + b \cos(w_{2}t) \right]$$

$$+ k_{2} \left[ \frac{a^{2}}{2} \left\{ 1 + \cos(2w_{1}t) \right\} + \frac{b^{2}}{2} \left\{ 1 + \cos(2w_{2}t) \right\} + \frac{b^{2}}{2} \left\{ 1 + \cos(2w_{2}t) \right\} + \frac{ab}{2} \left\{ \cos(w_{1} + w_{2})t + \cos(w_{1} - w_{2})t \right\} \right]$$

$$+ k_{3} \left[ \frac{\frac{3}{4}a^{3} \cos(w_{1}t) + \frac{3}{2}ab^{2} \cos(w_{1}t) + \frac{a^{3}}{4}\cos(3w_{1}t) + \frac{a^{3}}{4}ab^{2} \cos(w_{1} - 2w_{2})t + \frac{3}{4}a^{2}b\cos(2w_{1} - w_{2})t + \frac{3}{2}a^{2}b\cos(w_{2}t) + \frac{3}{4}b^{3}\cos(w_{2}t) + \frac{b^{3}}{4}\cos(3w_{2}t) + \frac{3}{4}a^{2}b\cos(2w_{1} + 2w_{2})t + \frac{3}{4}ab^{2}\cos(w_{1} + 2w_{2})t \right]$$

$$(2.47)$$

therefore, the output signal has several frequency components in its spectrum. Amplitudes of various components are listed in Table 2.1.

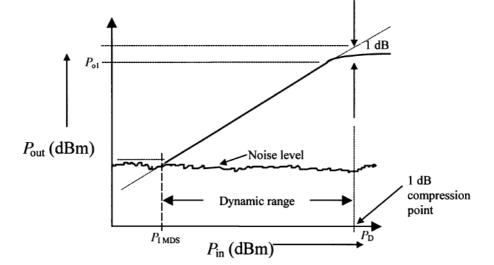

Figure 2.10 illustrates the input-output characteristics of an amplifier. If input signal is too low then it may be submerged under the noise. Output power rises linearly above the noise as the input is increased. However, it deviates from the linear

| Harmonic Components     | Amplitude                                                 |  |

|-------------------------|-----------------------------------------------------------|--|

| $\omega_1$              | $k_1a + k_3\left(\frac{3}{4}a^3 + \frac{3}{2}ab^2\right)$ |  |

| $\omega_2$              | $k_1b + k_3\left(\frac{3}{4}b^3 + \frac{3}{2}a^2b\right)$ |  |

| $\omega_1 - \omega_2$   | $k_2 \frac{ab}{2}$                                        |  |

| $\omega_1 + \omega_2$   | $k_2 \frac{ab}{2}$                                        |  |

| $2\omega_1$             | $k_2 \frac{a^2}{2}$                                       |  |

| $2\omega_2$             | $k_2 \frac{b^2}{2}$                                       |  |

| $3\omega_1$             | $k_3 \frac{a^3}{4}$                                       |  |

| 3 <i>w</i> <sub>2</sub> | $k_3 \frac{b^3}{4}$                                       |  |

| $2\omega_1 - \omega_2$  | $\frac{3}{4}k_{3}a^{2}b$                                  |  |

| $\omega_1 - 2\omega_2$  | $\frac{3}{4}k_3ab^2$                                      |  |

| $2\omega_1 + \omega_2$  | $\frac{3}{4}k_{3}a^{2}b$                                  |  |

| $\omega_1 + 2\omega_2$  | $\frac{3}{4}k_3ab^2$                                      |  |

Table 2.1: Amplitudes of various harmonics in the output

Figure 2.10: Gain characteristics of an amplifier

characteristic after a certain level of input power. In the linear region output power can be expressed in dBm as follows:

$$P_{out}(dBm) = P_{in}(dBm) + G(dB)$$

(2.48)

The input power for which output deviates by 1dB below its linear characteristic is known as 1-dB compression point. In this figure, it occurs at an input power of  $P_D$  dBm that produces an output of  $P_{o1}$  dBm. From the above relation, we find that

$$P_{o1}(dBm) + 1 = P_D(dBm) + G(dB)$$

(2.49)

or,

$$P_{D}(dBm) = P_{o1}(dBm) + 1 - G(dB)$$

(2.50)

The difference between the input power at 1-dB compression point and the minimum detectable signal defines the dynamic range (DR). Hence [8],

$$DR = P_D(dBm) - P_{IMDS} \tag{2.51}$$

#### 2.6. EFFICIENCY

The drain efficiency is defined as the ratio of RF output power to dc input power, so rises in roughly the same proportion as the fundamental output power if the dc power is constant. The degree of correlation depends on the relative contributions of the harmonics to the total RF output power, and the degree by which the dc input power changes as the device enters saturation. The efficiency is an important parameter in power amplifier design. The power-added efficiency is defined by

$$\eta_{PA} = \frac{\left(P_{OUT} - P_{IN}\right)}{P_{DC}} \tag{2.52}$$

and measures the incremental RF power added by the device, comparing the output power to the level of input power needed to achieve it. This measure of efficiency depends on the gain of the device since  $P_{OUT} = GP_{IN}$ . It is a useful performance measure in amplifier design because it tells us the relative contribution and cost made by the device to enhancing power levels [9].

## 2.7. SUMMARY

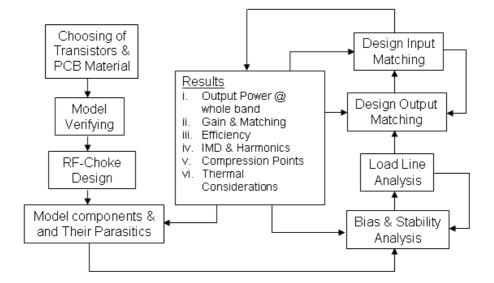

This chapter explains non-linear design methods of a broadband power amplifier in theoretically. It is important to understand the theoretical part, because of getting ability to comment the results, and also finding a suitable solution for a problem that is appeared. Design process of power amplifier follows the steps that is seen from the below flow chart.

Figure 2.11: Flow chart of the power amplifier design process

As seen from above flow chart, the design is started with choosing of RF power transistor that is used in both the driver stage and the last stage. RF power transistor technology is searched and according to specifications of our design, useful one (Si LDMOS) is chosen. The reasons of choosing this technology will be mentioned at Chapter III. Choosing the printed circuit board material is very crucial because of the operating frequency band of the design. Dielectric constant, loss tangent, and processability of PCB material (i.e. for example through hole plating) are the criterias to make a decision of choosing the suitable PCB material. After choosing the transistors and PCB material, the design process is started.

Initially, RF-Choke is designed, and according to the measurement results, the components and their parasitics are modeled to simulation. Then, biasing and stability, and load line analyses are done sequentially. These analyses are too related to each other; so after analyzing the load line, it is needed to return to analyzing of biasing and stability. Finally, we design the input and output matching network; design of output matching network is done first, then the input matching network is designed, then the output matching network is designed again, as a result the design process of matching networks follows these loop two or three times. Finally we are able to get the simulation and measurement results; biasing and stability analysis, designing of input and output matching networks and finally modeling of components and their parasitics are done again. To achieve the best performance at the whole frequency band, these processes are done several times by following the steps that is seen in Figure 2.11.

The design and non-linear modeling process of 500MHz-2GHz power amplifier will be mentioned thoroughly in the following chapters.

# **CHAPTER III**

# TRANSISTOR TECHNOLOGIES

There are lost of transistor technologies exist in the market. This chapter gives brief information about transistor technologies that are mostly used. These are the semiconductor technologies:

1. Silicon

1.1. Silicon CMOS

1.2. Silicon LDMOS

2. Gallium Arsenide

2.1. GaAs MESFET

2.2. GaAs PHEMT

2.3. GaAs MHEMT

2.4. GaAs HBT

3. Indium Phosphide

3.1. InP HEMT

3.2. InP HBT

4. Silicon carbide

4.1. SiC MESFET

4.2. SiC LDMOS

5. SiGe HBT

6. GaN HEMT

#### 3.1. SILICON

Silicon is the most common metalloid. As the eighth most common element in the universe by mass, silicon very rarely occurs as the pure free element in nature, but is more widely distributed in dusts, planetoids and planets as various forms of silicon dioxide (silica) or silicates. On Earth, silicon is the second most abundant element (after oxygen) in the crust, making up 25.7% of the crust by mass.

Silicon has many industrial uses. Elemental silicon is the principal component of most semiconductor devices, most importantly integrated circuits or microchips. Silicon is widely used in semiconductors because it remains a semiconductor at higher temperatures than the semiconductor germanium and because its native oxide is easily grown in a furnace and forms a better semiconductor/dielectric interface than any other material [10].

#### 3.1.1. Silicon CMOS

CMOS provides lower cost advantage. It is capable of producing a small die size because of the small geometries used in advanced CMOS processing. The advantage in total die size offered by CMOS is a function of the ratio of the digital to analog areas of the design. Design with a large digital to analog ratios typically benefits most from the lower geometries of CMOS.

CMOS processes have good linearity across voltage. However, it processes usually do not have the same quality of noise performance as the same sized geometry of other technologies processes [11]. CMOS is used in low power amplification processes, especially in cellular phone applications.

Attributes:

- Silicon is so cheap.

- It comes in 12 inch (300 mm) and bigger wafers.

- Processing is cheap. But it is not a good media for microstrip (lossy).

- Silicon by itself doesn't make very good amplifiers above 10 GHz.

- Noise figure and power are all second class to any of the compound semiconductors.

- It can only operate reliably up to 100°C, but silicon is a pretty good heat dissipater [12].

#### 3.1.2. Silicon LDMOS

The recent surge in wireless communication services has created a huge demand for cost-effective, high gain, ultra-linear high power RF transistors for use in base station power amplifiers. Traditionally, RF power transistors have been built using Si bipolar technology, although GaAs power transistors are also available. Recently, laterally diffused metal-oxide-semiconductor (LDMOS) transistors have been proven to be very popular for these applications. They have superior RF performance compared to bipolar transistors and are highly cost-effective compared to their GaAs counterparts.

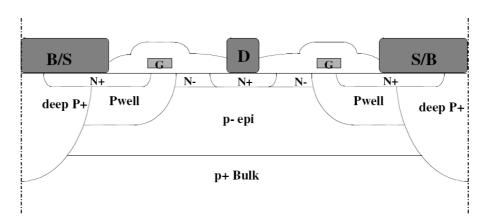

The cross-section of a typical LDMOS transistor is shown in Figure 3.1 The device has a high doped p-type sinker diffusion, used to ground the Source to the substrate. This eliminates the need for an external connection from Source to the ground, and hence minimum common lead inductance and maximum RF gain. The p-type body region under the Gate forms the channel. Devices have been fabricated to operate from 3 volts up to 48 volts on the Drain. Higher breakdown voltages are accomplished in LDMOS devices by the Lightly Doped Drain (LDD) region, also called the drift region. In absence of the LDD region, most of the applied voltage

appears across Gate oxide and leads to breakdown by impact generation in the substrate region. This results in a specific breakdown voltage for a given oxide thickness. Hence, the Drain is receded away from the Gate by formation of an LDD region between the Gate and Drain edges. The LDD is carefully designed to support a uniform electric field during breakdown. Figure 3.2 shows the path for current flow in the transistor when a Gate bias higher than threshold voltage is applied. It can be noticed that the current flow is in a lateral direction and there is no significant current crowding in the channel region.

Figure 3.1: Cross section of an LDMOS transistor

Figure 3.2: Current path in an LDMOS transistor ( $V_{GS} > V_{th}$ )

LDMOS transistors have a major advantage compared to bipolar transistors because of their "immunity" to thermal runaway. An increase in die temperature causes an increase in the Source resistance and hence reduced current flow [13].

Although some vendors offer RF versions of DMOS, its vertical structure has serious problems with excessive parasitic capacitance starting at around 500 MHz. LDMOS fares much better at higher frequencies, not least due to extensive technology development recent years. LDMOS components with output power over 100 Watts at 2.7 GHz are available at the moment.

High power LDMOS devices typically provide internal impedance matching for intended frequency band. The practical power limit for LDMOS without internal matching is around 10 Watts at 2.5 GHz. This might leave a window of opportunity for other materials in broadband power designs. Wide bandgap materials offer higher output power per 1pF of gate capacitance, which is an advantage for broadband applications.

What is so special with LDMOS? As a device of MOSFET variety, LDMOS uses an inversion channel at the silicon-oxide interface. The inversion channel is induced under the gate by positive gate potential. Under practically relevant conditions the inversion layer only exists over the laterally diffused P-well, which is sometimes called depletion stopper. As the electrons leave the region over the stopper they are picked up by the electric field due to positive drain bias and abandon the inversion channel going deeper into the bulk. The effective gate length defines the lateral extension of the stopper layer. It may be therefore shorter than the physical length of the gate electrode.

High breakdown voltage of LDMOS is one of its most important advantages. For a given output impedance the power output is the square of voltage swing, therefore

you get over 7dB more power going from 12V to 28V  $V_{dd}$ . Even if you are able to match that low-voltage component you will lose some bandwidth and you will certainly need a lot of current out of your power supply. So why does LDMOS have higher operation voltage than silicon than GaAs MESFET if the breakdown field in GaAs is higher than in silicon? Examination of the cross-sections will give the answer to this question. Electric field crowding at the gate edge of the MESFET takes up all the advantages of the higher breakdown field of GaAs. In addition, the current pathway through the buffer layer does not offer the designer much choice apart from increasing the gate length to make a tradeoff between gain and output power. In LDMOS the depletion stopper and the field plate form a fairly uniform electric field plate has little effect on the breakdown in LDMOS, since the breakdown field of the oxide is much more over than that of silicon [14].

Table 3.1 summarizes the features of an LDMOS transistor that make it the technology of choice for present-day high power linear amplifiers [15], and Table 3.2 shows the features of some of the transistor technologies in comparison.

| Attribute          | Effective Parameter                                       | Benefit                                                                                   |

|--------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Higher gain        | High G <sub>m</sub> and low C <sub>rss</sub>              | Lower system cost due to fewer stages.                                                    |

|                    |                                                           | Increased gain can be traded for enhanced stability.                                      |

| Higher efficiency  | Low R <sub>DS(on)</sub> and low C <sub>oss</sub>          | Lower junction temperature for same output                                                |

|                    |                                                           | power, hence greater system performance and                                               |

|                    |                                                           | higher MTBF.                                                                              |

| Greater stability  | Low C <sub>rss</sub> and very low<br>Source inductance    | Easier design.                                                                            |

| Simplicity of use  | High input resistance,                                    | Very little Gate current, hence simple                                                    |

|                    | single supply, and backside                               | Gate bias circuits. Dual supply sources                                                   |

|                    | Source contact                                            | not needed.                                                                               |

| Improved linearity | $\boldsymbol{I}_{D(sat)}$ and $\boldsymbol{G}_m$ flatness | Less output distortion, reduced overall system<br>power for the same degree of linearity. |

Table 3.1: Features of LDMOS Transistors

|                           | MESFET/HEMT      | III-V HBT        | Si BJT                | Si:Ge HBT        | Power MOSFET<br>(LDMOS) |

|---------------------------|------------------|------------------|-----------------------|------------------|-------------------------|

|                           |                  | Low Voltage R    | elated Characteristic | s                |                         |

| Parasitic loss            | Very good        | Very good        | Moderate              | Moderate         | Moderate                |

| Single-polarity<br>supply | No               | Yes              | Yes                   | Yes              | Yes                     |

| Power added<br>efficiency | Excellent        | Very good        | Moderater             | Moderate         | Good for f<~2 GHz       |

| Linearity                 | Excellent        | Very good        | Moderate              | Very good        | Moderate                |

| Power density             | Moderate         | Excellent        | Very good             | Excellent        | Moderate                |

|                           |                  | General          | Characteristics       |                  |                         |

| Cost                      | Moderate to high | Moderate to high | Low to moderate       | Moderate to high | Low to moderate         |

| Maturity                  | Good             | Good             | Excellent             | Moderate         | Very good               |

Table 3.2: Features of different transistor technologies

# **3.2. GALLIUM ARSENIDE (GaAs)**

Engineers estimate that within the next 10 to 15 years we will reach the limit, in terms of size and performance, of the silicon transistors key to the industry. As a result, they are working on new materials and technologies that may be able to reach beyond the limits of silicon. One such material is investigated a family of semiconductors known as III-V compound semiconductors. Unlike silicon, these are composite materials. A particularly hot prospect is indium gallium arsenide, or InGaAs, a material in which electrons travel many times faster than in silicon. As a result, it should be possible to make very small transistors that can switch and process information very quickly. It is demonstrated by fabricating InGaAs transistors that can carry 2.5 times more current than state of the art silicon devices. More current is the key to faster operation [16].

Gallium arsenide (GaAs) is a compound of two elements, gallium and arsenic. It is an important semiconductor and is used to make devices such as microwave frequency integrated circuits (i.e., MMICs), infrared light-emitting diodes, laser diodes and solar cells. GaAs has some electronic properties which are superior to those of silicon.

- It has a higher saturated electron velocity and higher electron mobility, allowing transistors made from it to function at frequencies in excess of 250 GHz.

- Also, GaAs devices generate less noise than silicon devices when operated at high frequencies.

- They can also be operated at higher power levels than the equivalent silicon device because they have higher breakdown voltages.

These properties recommend GaAs circuitry in mobile phones, satellite communications, microwave point-to-point links, and some radar systems. It is used in the manufacture of Gunn diodes for generation of microwaves.

Another advantage of GaAs is that it has a direct bandgap, which means that it can be used to emit light efficiently. Silicon has an indirect bandgap and so is very poor at emitting light. (Nonetheless, recent advances may make silicon LEDs and lasers possible).

Silicon has three major advantages over GaAs for integrated circuit manufacture.

- 1. First, silicon is abundant and cheap to process. Si is highly abundant in the Earth's crust, in the form of silicate minerals. The economy of scale available to the silicon industry has also reduced the adoption of GaAs.

- 2. The second major advantage of Si is the existence of silicon dioxide (one of the best insulators). Silicon dioxide can easily be incorporated onto silicon circuits, and such layers are adherent to the underlying Si. GaAs does not form a stable adherent insulating layer.

3. The third, and perhaps most important, advantage of silicon is that it possesses a much higher hole mobility. This high mobility allows the fabrication of higher-speed P-channel field effect transistors, which are required for CMOS logic. Because they lack a fast CMOS structure, GaAs logic circuits have much higher power consumption, which has made them unable to compete with silicon logic circuits [17].

In the latest research, the researchers have improved the stability and electrical characteristics of the gate oxide, comprised of gallium oxide and gadolinium oxide. As a result, the current decreases only 1.5 percent after 150 hours of operation under extreme conditions. In contrast, the previously best research results reported a 22 percent drop over a three-hour period.

Currently, most wireless applications use gallium arsenide metal-semiconductor field-effect transistors (MESFETs), which lack a gate oxide, but which are necessary because higher frequencies are attainable with gallium arsenide compared to silicon. (That's because electrons can travel five to six times faster in gallium arsenide-based transistors.)

Because of the lower power consumption of gallium arsenide MOSFETs, the talk time for cellular phones would be extended. Meanwhile, wireless base stations would be more powerful and more efficient [18].

## 3.2.1. GaAs MESFET