# DIGITAL IMPLEMENTATION OF TRIGONOMETRIC FUNCTIONS VIA FPGA DEVICES

Shakir Salman Ahmad

DECEMBER, 2017

# DIGITAL IMPLEMENTATION OF TRIGONOMETRIC FUNCTIONS VIA FPGA DEVICES

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF ÇANKAYA UNIVERSITY

BY SHAKIR SALMAN AHMAD

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER

IN

## THE DEPARTMENT OF

# ELECTRONIC AND COMMUNICATION ENGINEERING

DECEMBER, 2017

Title of the Thesis

# : DIGITAL IMPLEMENTATION OF TRIGONOMETRIC FUNCTIONS VIA FPGA DEVICES

## Submitted by SHAKIR SALMAN AHMAD

Approval of the Graduate School of Natural and Applied Sciences, Çankaya University.

Prof. Dr. Can COĞUN Director

I certify that this thesis satisfies all the requirements by way of thesis for the degree of Master of Science.

Prof. Dr. Sıtkı Kemal İDER

Head of Department

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, by way of thesis for the degree of Master of Science.

Assoc. Prof. Dr. Orhan GAZİ Supervisor

Examination Date: 19.12.2017

**Examining Committee Members**

Assoc. Prof. Dr. Orhan GAZİ Assist. Prof. Dr. Javad RAHABI (Turkish Aeronautical

(Çankaya Univ.) Association Univ.) (Çankaya Univ.)

Assist. Prof. Dr. Göker ŞENER

# STATEMENT OF NON-PLAGIARISM PAGE

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, by way of required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name, Last Name : Shakir Salman Ahmad

Signature

الك :2

Date

: 19.12.2017

#### ABSTRACT

# DIGITAL IMPLEMENTATION OF TRIGONOMETRIC FUNCTIONS VIA FPGA DEVICES

AHMAD, Shakir Salman

M.Sc., Department of Electronics and Communication Engineering

Supervisor: Assoc. Prof. Dr. Orhan GAZİ

December. 2017, 52 Pages

As the technology improves, the importance of dynamic hardware design gains more and more attention in the scientific world. FPGA devices are used for digital circuit design purposes, and recently a significant improvement has been observed in FPGA technology. Many communication systems employed in wireless and satellite systems employ FPGAs.

Trigonometric functions, such as sine or cosine, are vital components of communication systems. With the invention of coordinate rotation digital computer, i.e., CORDIC in short, algorithm in 1956, it became possible to generate the trigonometric functions in digital devices, such as calculators, microcontrollers, and electronic chips etc.

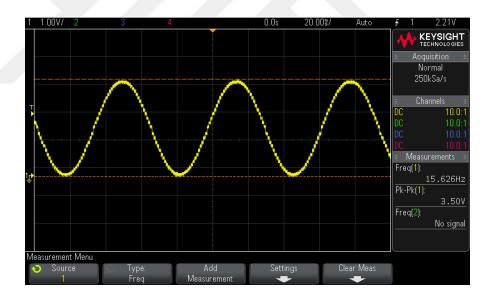

In this thesis work, we first implement the CORDIC algorithm in MATLAB environment, and analyze the iteration number of the algorithm considering the accuracy of the calculated sine or cosine value. Next, we implement the CORDIC algorithm in FPGA environment using the VHDL programming language. For this purpose, we used the FGPA board involving SPARTAN-3 FPGA chip produced by the XILINX company. Later, we followed an alternative approach for the generation of sine signal. For this purpose, we generated 1Hz sine signal in MATLAB and considering the ratio among sine samples, we generated an integer sequence keeping approximately the same ratio among samples, and using this integer sequence we generated sine signal in FPGA platform and using the D/A converter, we observed the generated sine signal on OSCILLOSCOPE screen. With this alternative approach, it became possible to generate sine signal with any frequency and much less hardware complexity. To generate different sine signals with different frequencies, we divide the clock of the FPGA device by a desired amount and use it while sending the sine samples to the output port.

Keywords: Cordic algorithm, FPGA, VHDL, and Cosine function

# ÖZET

# FPGA CİFAZLARI İLE TRİGONOMETRİK FONKSİYONLARIN DİJİTAL GERÇEKLEŞTIRİMİ

AHMAD, Shakir Salman

YL, Elektronik ve Haberleşme Mühendisliği Bölümü

Danışman: Doçent Dr. Orhan GAZİ

#### Aralık 2017, 52 Sayfa

Teknolojinin gelişimi ile birlikte dinamik donanım yapılarının tasarlanması gün geçtikçe daha da önem kazanmaktadır. FPGA cihazları dinamik donanımlar tasarlanmak için kullanılan ve gittikçe dünyada popülaritesi artan elektronik ünitelerdir. FPGA cihazları günümüzde birçok kablosuz ve uydu iletişim sistemlerinde kullanılmaktadır.

Sinüs ve kosinüs gibi trigonometrik fonksiyonlar iletişim sistemlerinin vazgeçilmez unsurlarıdırlar. CORDIC algoritmasının 1956 yılında icadı ile trigonometrik fonksiyonların sayısal elektronik cihazlarındaki gerçekleştirimlerinin önü açılmıştır. Bugün günümüzde kullanılan birçok elektronik cihaz, mesela hesap makinesi, mikrokontroller ve elektronik yongalar CORDIC algoritmasını kullanmaktadır.

Bu tez çalışmasında ilk olarak CORDIC algoritmasının MATLAB ortamında gerçekleştirimini yapıyoruz ve algoritmada kullanılan yineleme sayısı ile elde edilen sinüsün veya kosinüsün gerçek değerinden ne kadar sapma gösterdiğini inceliyoruz. Daha sonra ise algoritmayı FPGA ortamında VHDL programlama dili kullanarak gerçekleştiriyoruz. Bunun için XILINX firmasının üretmiş olduğu SPARTAN-3 yonga içeren FPGA platformu kullanıyoruz. Tezin üçüncü çalışmasında sinüs veya kosinüs sinyallerini üretmek için daha basit bir yol takip ediyoruz. Bunun için frekansı 1Hz olan sinüs veya kosinüs sinyallerinin bir periyodunu MATLAB ortamında üretiyoruz. Daha sonra üretilen sayılar arasındaki oranı göz önüne alarak bir tam sayı dizini oluşturuyoruz. Oluşturulan tam sayı dizinini FPGA ortamında taşıyarak VHDL dili ile FPGA cihazının saat darbe sayısı istediğimiz gibi ayarlayarak herhangi bir frekansa sahip olan sinüs veya kosinüs sinyalini üretiyoruz. Kullandığımız bu yöntem CORDIC algoritmasına göre daha basit ve donanım karmaşıklığı çok daha az olmaktadır.

Anahtar kelimeler: Cordic Algoritması, FPGA, VHDL, Kosinüs fonksiyon.

# ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to Assoc. Prof. Dr. Orhan GAZİ for his supervision, special guidance, suggestions, and encouragement through the development of this thesis.

It is a pleasure to express my special thanks to my family for their valuable support.

# TABLE OF CONTENTS

| ABSTR                                  | ACTIV                             |  |  |  |

|----------------------------------------|-----------------------------------|--|--|--|

| ÖZET                                   | VI                                |  |  |  |

| ACKNC                                  | WLEDGEMENTS                       |  |  |  |

| TABLE                                  | OF CONTENTSIX                     |  |  |  |

| LIST OF                                | FIGURESXI                         |  |  |  |

| СНАРТ                                  | ER ONE                            |  |  |  |

| INTRO                                  | DUCTION TO ISE SUITE 1            |  |  |  |

| 1.2.                                   | OVERVIEW OF ISE                   |  |  |  |

| 1.2.1. F                               | Project Navigator Interface2      |  |  |  |

| 1.3.                                   | Design Panel2                     |  |  |  |

| 1.3.1.                                 | Sources View2                     |  |  |  |

| 1.3.2.                                 | Processes View3                   |  |  |  |

| 1.3.3.                                 | Files Panel5                      |  |  |  |

| 1.3.4.                                 | Libraries Panel5                  |  |  |  |

| 1.3.5.                                 | Console Panel5                    |  |  |  |

| 1.3.6.                                 | Errors Panel5                     |  |  |  |

| 1.3.7.                                 | Warnings Panel5                   |  |  |  |

| 1.3.8.                                 | Workspace5                        |  |  |  |

| 1.4.                                   | ISE Console window                |  |  |  |

| 1.5. ISE                               | Reports/Edit window               |  |  |  |

| СНАРТ                                  | ER TWO 7                          |  |  |  |

| FUNDA                                  | MENTAL OF VHDL AND FPGA7          |  |  |  |

| 2.1. DEFINITION AND BACKGROUND ON VHDL |                                   |  |  |  |

| 2.1.1. L                               | Design Flow in VHDL8              |  |  |  |

| 2.1.2.                                 | Code Structure in VHDL9           |  |  |  |

| 2.2. DEI                               | FINITION AND BACKGROUND ON FPGA10 |  |  |  |

| 2.2.1.                                 | FPGA Application11                |  |  |  |

| 2.2.2.                                 | Advantages of FPGA13              |  |  |  |

| СНАРТ                                  | ER THREE                          |  |  |  |

| FUNCTION CALCULATION USING CORDIC            | 14  |

|----------------------------------------------|-----|

| 3.1. TRIGONOMETRIC FUNCTIONS                 | 14  |

| 3.2. NUMERICAL EXAMPLE FOR CORDIC            | 18  |

| CHAPTER FOUR                                 | 23  |

| IMPLEMENTING CORDIC IN FPGA USING VHDL       | 23  |

| 4.1. OVERVIEW OF CORDIC ARCHITECTURES        | 23  |

| 4.2. FPGA IMPLEMENTATION TO CORDIC ALGORITHM | 25  |

| CHAPTER FIVE                                 | 27  |

| GENERATION OF SINUSOIDAL SIGNALS             | 27  |

| 5.1. DIGITAL TO ANALOG CONVERTER             | 27  |

| SIMULATION AND RESULT                        | 29  |

| 5.2. INTRODUCTION                            | -   |

| 5.2.1. Getting Started                       | .29 |

| 5.3. BEHAVIORAL SIMULATION USING ISIM        |     |

| 5.3.1. How to open project                   | .31 |

| 5.4. How to add an HDL Test Bench            |     |

| 5.5. Behavioral Simulation Using ISim        | .33 |

| 5.6. INFORMATION FROM VHDL TEST BENCH        | 38  |

| 5.7. How to set-up and test NEXYS3 board     | 38  |

| 5.8. SWITCHES AND 7-SEGMENTS DISPLAYS        | 39  |

| 5.8.1. LEDs                                  | .40 |

| 5.8.2. Seven Segment Displays                | .41 |

| 5.8.3. Switches                              | .41 |

| 5.8.4. Push Buttons                          | .42 |

| CHAPTER SIX                                  | 52  |

| CONCLUSIONS AND FUTURE WORKS                 | 52  |

| REFERENCES                                   | 53  |

|                                              |     |

# LIST OF FIGURES

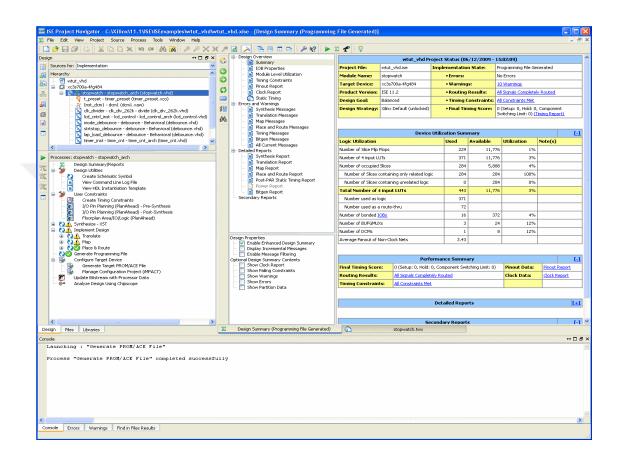

| Figure 1: Project Navigator                                       | 3   |

|-------------------------------------------------------------------|-----|

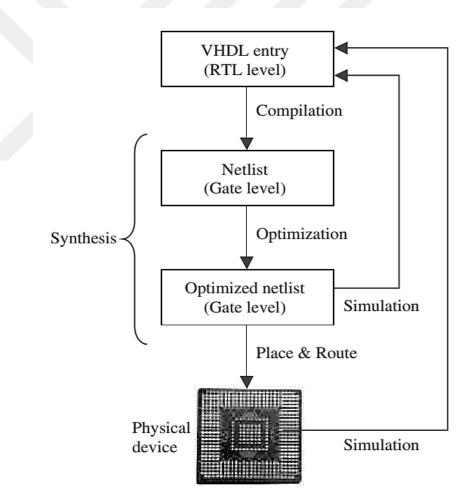

| Figure 2 Design Flow Summarization.                               | 8   |

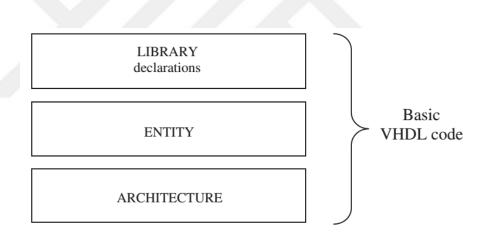

| Figure 3. VHDL Code Components                                    | 9   |

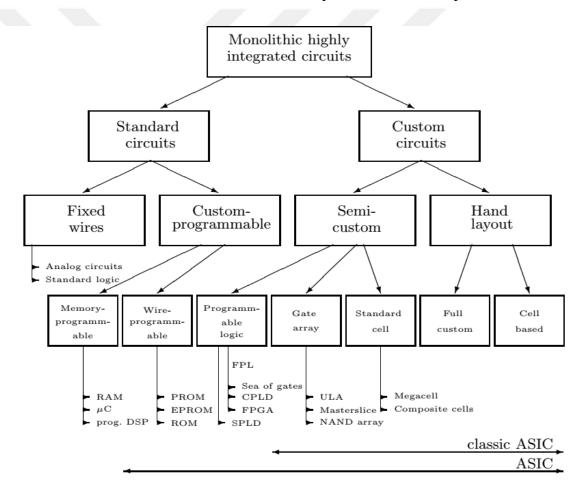

| Figure 4 Classification of VLSI circuits                          | .11 |

| Figure 5 A field-programmable gate array architecture             | .12 |

| Figure 6 CORDIC representation using rotation mode                | .15 |

| Figure7 number of iterations and angles                           | .20 |

| Figure8 iteration with error ratio                                | .22 |

| Figure 9 Basic Architecture of CORDIC                             | .24 |

| Figure 10 Nexys 3 <sup>™</sup> FPGA Board Reference               | .25 |

| Figure 11 Digital to Analog Converte                              | .28 |

| Figure 12 How to create design file.                              | .30 |

| Figure 13. Project navigator window                               | .31 |

| Figure 14 Explain choices Implementation and Simulation options   | .31 |

| Figure 15.creat test bench                                        | .32 |

| Figure 16 To save test bench file                                 | .33 |

| Figure 17. How to select ISim                                     | .34 |

| Figure 18 How to select Simulate Behavioral Model                 | .35 |

| Figure 19. Change properties and behavioral simulation properties | .36 |

| Figure 20. How to perform simulation                              | .37 |

| Figure 21 Setup NEXYS3 board                                      | .39 |

| Figure 22 Connection from LEDs to NEXYS 3 Board                   | .40 |

| Figure23 Results of cosine values                                 | .43 |

| Figure24 cosine wave                                              | .45 |

| Figure 25 Cosine wave with shift                                  | .45 |

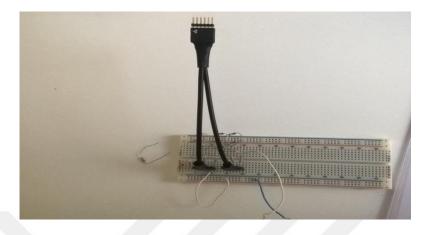

| Figure 26 R-2R ladder                                             | .50 |

| Figure 27 practical circuit                                       | .50 |

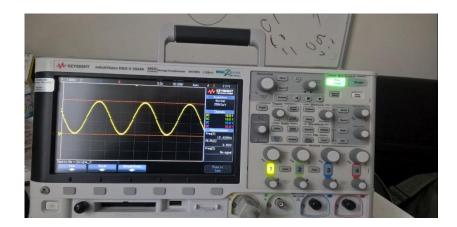

| Figure 28The waveform we generated it.                            | .51 |

| Figure 29 sine wave                                               |     |

|                                                                   |     |

#### **CHAPTER ONE**

#### **Introduction to ISE Suite**

## **1.1.Definition and Background**

"Xilinx ISE (Integrated Synthesis Environment)" is a software tool produced by Xilinx for synthesis and analysis of HDL designs, enabling the developer to synthesize ("compile") their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different motivations, and configure the target device with the programmer.

Xilinx ISE is a software development platform for FPGA supplied from Xilinx, and it was tightly-coupled to the architecture of given chips, and cannot be used with FPGA products from other retailers. The Xilinx ISE is fundamentally utilized for circuit design and synthesis, while ISIM or the ModelSim logic simulator is utilized for framework level analysis. Different parts dispatched with the Xilinx ISE include the a Software Development Kit (SDK), Embedded Development Kit (EDK), and ChipScope Pro.

Since 2012, Xilinx ISE has been stopped for VDS, that aids the same roles by way of ISE with extra highlights for framework on a chip progression. Xilinx released the last version of ISE in October 2013 (version 14.7), and states that "ISE" has moved into the supporting period of its item life cycle, and there are not any more arranged ISE out.

#### **1.2.** Overview of ISE

All parts of design flow are controlled by ISE. Through the interface of Project Navigator (PG)ö we can get the majority of the tools implementation design and entry design. By this way, we can get files and documents related with our project.

#### **1.2.1. Project Navigator Interface**

Practically the Interface of Project Navigator is classified into four types of panel sub-windows as explained in Figure 1. On the top-left of screen we see file, design and libraries panel are displayed and they lead to source file of the project. At the lower part of the Project Navigator we have the console, warnings and errors which show status messages' warnings and errors. We see the multi-document- interface (MDI) window indicate to workspace. We can use it to show schematics, text files, design reports, and simulation of waveforms. Every window might be resized, undocked from PN, moved to another area inside the fundamental PG window, tiled, layered, or shut. Boards might be opened or shut by utilizing the View then Panels then menu choices.

#### 1.3. Design Panel

#### **1.3.1.** Sources View

We can see the name of project by the sources view in order to display the name of project documents of user the required device and source of design files related with design view choices. The Design View ("Sources for") drop-down rundown at the highest point of the Sources tab enables you to see just those source documents related with the design view we choose, for example, Synthesis/Implementation or Simulation.

Every file has an icon referring to the type file (HDL, text, core, schematic). In order to know the source type and their related icons we can use help in  $ISE^{TM}$ . For this purpose we can chose help and then select help contents. And search about "source file type" after click on index tab. The sign '+'on the icon of the file refers to it has more than one level of hierarchy and we can open these levels. We can expand and show the

contains of the file by click on the sign '+'and the file will be opened by indicating on the file name then double click.

#### Figure 1: Project Navigator

#### 1.3.2. Processes View

The Processes view is important context and we can change its state depending on what we choose of the source type in sources part and top-level of source in our project. By this way, we choose the necessary function for setting, in order to run our design and analyzing. By using processes, we get several functions such as:

1-Report or design summary.

We can access the report of design and results data and message from summary design.

2- Utilities of design.

We can access from utilities of design create schematic symbol, view command log file and view HDL instantiation template.

3- Users constraints.

We get several branches such as: create timing constraints, I/O pin planning (planned Ahead)-pre synthesis, I/O pin planning (planned Ahead)-post synthesis and floor plan areal /IO/logic (planned Ahead).

4- Syntheses

Synthesis contains many parts such as: view of RTL (register transfer level) schematic, view technology schematic, check syntax and great post- synthesis simulation model.

5- Implement design.

Implement of design part contains several levels

A- Translate.

Translate contains generate post-translate simulation model.

B- Map

Map contains several levels: Generate post-map static timing, analyze post-map static timing, manually place and route (FPGA Editor) and generate post-map simulation model.

C- Place and Route.

Place and Route panel has several types such as: Generate post-place and route static timing, analyze post-place and route static timing, analyze timing/floor plan design (plan Ahead), view/edit routed design (FPGA Editor), Analyze power distribution (x power Analyzer), Generate text power report, generate post-place and route simulation model, Generate IBIS model, view IBIS model, Back-annotate pin locations, view locked pin constraints and generating programming file.

D-Configure target device.

Configure target device contains: generate target PROM/ACE file, manage configuration project (IMACT) and analyze design using chip scope.

### 1.3.3. Files Panel

We get a list of flat sortable source files in our project from the files panel. We can have sorted these file in view by any columns, we can modify and view properties to every file by selecting the option source properties after indicating the file and right clicking on it.

#### 1.3.4. Libraries Panel

HDL libraries and related source files of HDL can be managed by the tab of libraries we can get, show the libraries and edit their libraries related with sources.

#### **1.3.5.** Console Panel

From project navigator and from run process, the Console panel gives us all output in standard state. We see error in symbol (x) in red color and yellow color for warning in symbol (i) with information about warning by way of a message.

#### **1.3.6.** Errors Panel

Only messages of error have been displayed here. Other massages are neglected out consol.

#### 1.3.7. Warnings Panel

If we have error of synthesis or message in console panel of warning or errors to location of error in HDL file. We select the messages of errors or by right click and chose the option go to source then HDL file will open and the indicator transfer to line where the errors lies. Only messages of warning displayed in this panel. Other console messages are neglected out. We can go to http://www.xilinx.com/support website to find answer to our problems and errors

#### 1.3.8. Workspace

The Workspace refers to the place of design editors with viewers with analysis tools when it is opened. ISE Text Editor, Schematic Editor, Timing Constraint Editor, Design Summary & Report Viewer, RTL and Technology Viewers, and Timing Analyzer are included. Other tools such by way of Plan Ahead for I/O planning and floor planning, ISE Simulator (ISim), 3rd party Text Editors, XPower Analyzer, and iMPACT open in separate windows outside the main PN environment when invoked.

#### **1.3.9.** Report Viewer & Design Summary

We get a summary of main design data from design summary also get all the reports and message from implementation and synthesis tools and gives important information about our project and we can overview information summary of device utilization performance data collected from place and route report summary and constraint information from all reports individual links.

#### **1.4.** ISE Console window

The ISE console window provides narrative from the design processes by way of they operate. Most of the scripts that the ISE runs and messages that are emitted by the various processes can be gotten by way of a running display in the Console window—seeing it while a design is being treated can be quite informative. Infrequently, some message will flash by and trigger an insight into a design's characteristics or defects. When the processing of a design has ended or finished, the "Errors" or "Warnings" tab will filter all of the process dialog down to the important details.

#### **1.5. ISE Reports/Edit window**

This shows a viewer for the numerous reports produced in the Processes window. It also becomes a very useful syntax-coloring editor for Verilog and VHDL sources in the Sources window.

## **CHAPTER TWO**

#### Fundamental of VHDL and FPGA

#### 2.1. Definition and Background on VHDL

VHDL means VHSIC Hardware Description Language. VHSIC is itself acronym to "Very High Speed Integrated Circuits" furnished through United States Department of Defense in 1980s. It is a language to a hardware description. It is a language to a system or electronic circuit behavioral description. It is the language for circuit simulation in addition to circuit synthesis [2].

Its early version is VHDL 87, next developed to a so-called VHDL 93. It is the first hardware description language and innovative standardized via Institute of Electrical and Electronics Engineers with IEEE 1076 standard. Furthermore, IEEE 1164, has been added to present a multi-valued logic system.

A major encouragement inspiration for utilizing VHDL (or its competitor, Verilog) is that VHDLs are a standard, technology/vendor standalone language, and is to portable and reusable. VHDL have two topmost instantaneous applications that are: 1) to area of ASICs (Application Specific Integrated Circuits) 2) To area of Programmable Logic Devices that comprising FPGAs—Field Programmable Gate Arrays and CPLDs—Complex Programmable Logic Devices. VHDL codes are written for two purposes: 1) it used to manufacture a chip of ASIC or to carry out circuit inside a programmable device such as Xilinx, Atmel and Altera. Presently, numerous

multifaceted marketable chips have been designed utilizing this approach, e.g., microcontrollers.

# 2.1.1. Design Flow in VHDL

As explained previously, VHDL is mainly used for synthesis in FPGA or in PLD or in ASIC. Design flow of VHDL is given in Figure 2 [2]. VHDL codes are saved in a file with extension .vhd and they have similar name as that of ENTITY's name. Compilation is primary stage of a synthesis process [2].

Figure 2 Design Flow Summary [2].

It is a high-level VHDL language that defines every circuit at Register Transfer Level (RTL) and feed it in a net list at gate level. Then, optimization is second step that is done

on gate-level. At this level, simulation of design is implemented. Lastly, it possible to generate a physical layout to a FPGA and PLD chips or generate covers to ASIC through place and-route (fitter) software

# 2.1.2. Code Structure in VHDL

VHDL code is comprised from three components [2]:

- 1. LIBRARY declarations: Covers a list of libraries that is utilized in design. Such as: ieee, std, work, etc.

- 2. ENTITY: Indicate I/O pins of a circuit.

- **3.** ARCHITECTURE: Comprises VHDL code that defines the way circuit should function.

Figure 3. VHDL Code Components [2]

To announce a LIBRARY and to make it visible to design; two lines of code required, one is the name of library, and the other indicating the name of the package to be used.

```

LIBRARY library_name;

USE library_name.package_name.package_parts;

```

An ENTITY is a list containing all input and output pins named as PORTS. Its syntax is given below.

```

ENTITY entity_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END entity_name;

```

ARCHITECTURE is an explanation that according to it a circuit should function. Its syntax is following:

```

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

```

#### 2.2. Definition and Background on FPGA

VLSI circuits have been categorized as shown in Fig. 2.3. FPGA member of a class of devices called field-programmable logic (FPL) [3]. FPLs describe programmable devices covering repetitive fields of elements and small logic blocks. It is seen that an FPGA is an ASIC technology of FPGAs application-specific ICs. Moreover, a design of a classic ASIC needs extra semiconductor dispensation stages essential to an FPL. Extra stages deliver higher-order ASICs in addition of energy consumption benefit but also with high Non-Recurring Engineering (NRE) expenses.

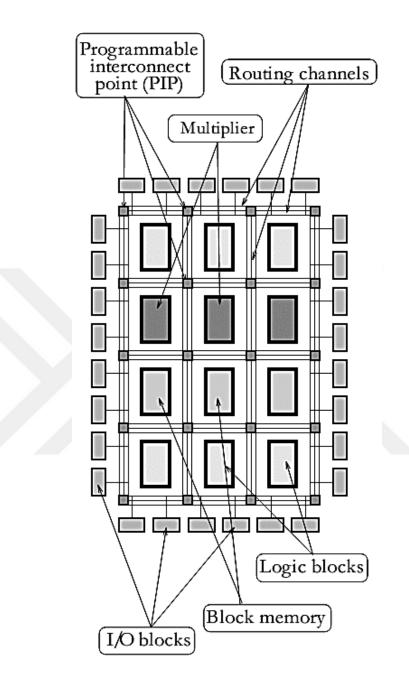

The architecture of FPGA device is given in Fig. 5. Fundamental logic blocks include 4 to 5-bit input tables, 1 or 2-bit output. Routing channel selections varies from short too long. Programmable I/O block with flip-flops is connected to physical boundary of device.

Traditionally, FPGA is not energy efficient, slower and usually given not much functional compared to their fixed ASIC counterparts. Nowadays, FPGAs by Altera

Stratix 5 have come to opposing like ASIC or Xilinx Virtex-7 and ASSP keys by giving considerably less power usage, higher speed, less resources cost, insignificant implementation real-estate, and more potentials to reconfiguration 'on- -fly'. Previously, a project is comprised 6 to 10 ASICs, now same project can be implemented utilizing only one FPGA [3].

# 2.2.1. FPGA Application

Any computable problem can be solved through FPGA. This is slightly established via fact of FPGA that is utilized to implement a soft microprocessor.

Figure 4 Classification of VLSI circuits [3]

FPGAs initially started as a competition to CPLDs to carry out glue logic to PCBs considering their size, abilities, and speed improved. The created multipliers inside FPGA architectures in late 1990s,

Figure 5 A field-programmable gate array architecture [3]

One more trend in utilizing of FPGAs is hardware acceleration is that it is possible to utilize FPGA to speed up given parts of algorithm and dividend part of calculation between FPGA and a generic processor.

Usually, FPGAs reserved to exact vertical applications where size of manufacture is not large. To these small size applications, premium that companies pay in hardware costs per unit to a programmable chips not less affordable compared to development resources consumed on making an ASIC to a small-size application. Nowadays, fresh cost and performance dynamics broadened variety of feasible applications.

#### 2.2.2. Advantages of FPGA

FPGAs have turned out to be extremely prominent in current years due to its abundance of benefits. FPGA enable parallel processing operations do be done reducing the computation overhead of complex algorithms. Programming time of FPGA can be considered small relative to its ASIC counterparts. Re-programmability property of the FPGAs provide us with great flexibility of circuit design.

NRE cost is zero: NRE denotes to one-time cost of investigating, developing, and testing a product. Since designing new **FPGAs** are re-programmable and can be utilized without any loss of quality every time, NRE cost is not present. This significantly decreases initial cost of manufacturing ICs since program is applied and verified on FPGAs free of cost. Due to look up table which used by FPGA technology, the execution time will be much less compared to ASIC technology. FPGAs are produced in great numbers, considering their benefits, they can be accepted as cheap in price and they are too friendly to the designer. In addition, power consumption is too less.

### **CHAPTER THREE**

#### **Function Calculation using CORDIC**

#### **3.1. Trigonometric functions**

Calculation of sine and cosine can be achieved via CORDIC. We start our discussion with those two simple functions to verify simplification of CORDIC. Differences between CORDIC classes not complicated in derivative and concept point of view, hence considering one or two classes can lead to other classes' derivation and calculation. Thereto, considering those classes will serve to provide details to one class of function and extension to another class.

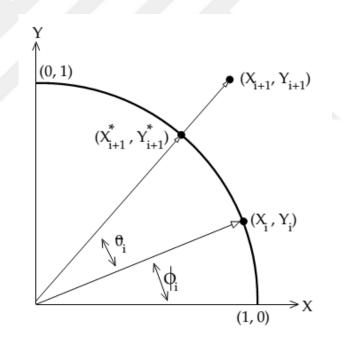

Sine and cosine calculations performed in rotation scenario and named by way of rotation mode. Rotating a (technically) is unit-length vector over any predetermined angle. Let us assume to calculate  $\cos \theta$  and  $\sin \theta$ , to give angle  $\theta$ . If we consider a vector  $(X_0, Y_0) \triangleq (1, 0)$ , rotate it on circle  $X^2 + Y^2 = 1$ , over a sequence of positive angles,  $\theta_0, \theta_1, \ldots, \theta_n$ , such that  $\theta_0 + \theta_1 + \cdots, \theta_n = \theta$ , and finish with vector  $(X_{n+1}, Y_{n+1})$ , then  $Y_{n+1} = \sin \theta$  and  $X_{n+1} = \cos \theta$ . Then, let us take look at rotation technique in CORDIC in rotation mode.

Figure 3.1 gives steps of rotation, by an angle  $\theta_i$ , of unit-length vector with coordinates  $(X_i, Y_i)$  at an angle  $\varphi$  from x axis. Coordinates,  $(X_{i+1}^*, Y_{i+1}^*)$ , of new vector given as:

$$X_{i+1}^* = \cos(\theta_i + \varphi)$$

$$X_{i+1}^{*} = \cos \varphi \cos (\theta_{i}) - \sin \varphi \sin (\theta_{i})$$

$$X_{i+1}^{*} = X_{i} \cos (\theta_{i}) - Y_{i} \sin (\theta_{i})$$

$$X_{i+1}^{*} = (X_{i} - Y_{i} \tan (\theta_{i})) \cos (\theta_{i})$$

$$Y_{i+1}^{*} = \sin(\theta_{i} + \varphi)$$

$$Y_{i+1}^{*} = \sin(\varphi)\cos(\theta_{i}) - \cos(\varphi)\sin(\theta_{i})$$

$$Y_{i+1}^{*} = X_{i}\cos(\theta_{i}) - Y_{i}\sin(\theta_{i})$$

$$Y_{i+1}^{*} = (X_{i} - Y_{i}\tan(\theta_{i}))\cos(\theta_{i})$$

Figure 3.1 Rotation mode CORDIC algorithm.

In CORDIC, rotation of  $(X_i, Y_i)$  to  $(X_{i+1}^*, Y_{i+1}^*)$ , is shown in Figure 3.1 and this rotation can mathematically be expressed as follows

$$X_{i+1} = X_i - Y_i \tan(\theta_i)$$

$$Y_{i+1} = X_i - Y_i \tan(\theta_i)$$

(3)

As we shall see below, utilization of a pseudo-rotation, in place of an exact rotation can reduce complexity and hardware implementation of the algorithm that is most important feature of CORDIC.

A comparison of Equations 1–2 and Equation 3 demonstrations that vector( $X_{i+1}, Y_{i+1}$ ), is lengthier than vector ( $X_{i+1}^*, Y_{i+1}^*$ ), by a factor of( $1/\cos \theta_i$ ). Consequently, to obtain  $\sin \theta$  and  $\cos \theta$  at end of final rotations of algorithm, it is important to multiply (scale) each  $X_i$  and  $Y_i$  by this factor. Then, if magnitudes of rotation angles are constant and total number of rotations also constant, nevertheless of given angle,  $\theta$  and thus, same situation with recurrences above if  $\theta_i$  suitably selected then multiplying of scaling factors is also constant. Thereto, rather than scaling by  $(1/\cos \theta_i)$  at each given step, i, to n + 1 iterations, it is adequate to simply multiply (scale) last out come by factor

$$k = \prod_{i=0}^{n} \frac{1}{\cos \theta_{i}},$$

$$k = \prod_{i=0}^{n} \sqrt{1 + \tan(\theta_{i})},$$

(4)

Actually, the last process, i.e., scaling by K can be avoided by setting  $X_0$  to the initial value1/K. This initial scaling in X subsequently introduces a similar scaling in Y.

Rotation by angle  $\theta_i$  can be converted into shifting by carefully selecting the rotations angles as will be explained now. Let us select  $\theta_i = \tan^{-1} 2^{-i}$ , this yields

$$X_{i+1} = X_i - Y_i 2^{-i}$$

$$Y_{i+1} = X_i - Y_i 2^{-i}$$

(5)

where  $2^{-i}$  signifies a simple shift to right by i bits, and the constant term is

$$k = \prod_{i=0}^{n} \sqrt{1 + 2^{-2i}} \,. \tag{6}$$

Last issue in this presentation is convergence. We might dive into points of interest of that beneath, however we make some preparatory comments here with a specific end goal to finish definition of algorithm.

In order to choose whether to add or subtract at the current iteration in the algorithm, total rotation angle so far is subtracted from  $\theta$ . If difference is negative, then an addition takes place; and if it is positive, then a subtraction takes place. Alternatively, we can look at the difference between the accumulated angle and target angle. If last rotation was to forward (backward), then next one can be backward (toward). In algorithm, the difference is calculated incrementally by way of  $\theta_0 \pm \theta_1$ ,  $\theta_0 \pm \theta_1 \pm \theta_2$ ,  $\theta_0 \pm \theta_1 \pm \theta_2 \pm \theta_3$ , etc. and preceding actions thereto correspond to making adjustments according to "how much farther we have to go". Angle residual is computed in a third variable  $Z_i$ .

To summarize, recurrences to computation of sine and cosine are done as

$$X_{0} = \frac{1}{k}, Y_{0} = 0, Z_{0} = \theta \text{ and } \theta_{i} = \tan^{-1} 2^{-i}$$

$$X_{i+1} = X_{i} - s_{i} 2^{-i} Y_{i}$$

$$Y_{i+1} = Y_{i} + s_{i} 2^{-i} X_{i}$$

$$Z_{i+1} = Z_{i} - s_{i} \theta_{i}$$

17

$$s_i = \begin{cases} 1 & if \ Z_i \ge 0\\ -1 & if \ Z_i \le 0 \end{cases}$$

# **3.2.** Numerical Example for CORDIC

In this section, a numerical example is given about rotation mode of CORDIC algorithm. We are going to evaluate sin and cos of the angle 0.735 radians.

First we need to find and set initial values of algorithms as:

$$Y_1 = 0$$

,  $Z_1 = 30^\circ \rightarrow 0.523$  rd,  $s_1 = +1$

$k = \prod_{i=1}^{10} \sqrt{1 + 2^{-2i}} = 1.1644$ ,  $X_1 = \frac{1}{k} = 0.8588$

Then, iterations are performed as follows:

For

$$i = 0$$

,

$\theta_0 = 0.7853 \ rd$

$X_2 = X_1 - s_1 \ 2^{-1} \ Y_1 \rightarrow X_2 = 0.8588 - 1 \times 2^{-1} \times 0 = 0.8588$

$Y_2 = Y_1 - s_1 \ 2^{-1} \ X_1 \rightarrow Y_1 = 0 + s_1 \ 2^{-1} \ X_1 = 0.4294$

$Z_1 = Z_0 - s_1 \ \theta_1 \rightarrow Z_1 = 0.523 - s_1 \ 0.7853 = -0.2623$

For

$$i = 1$$

,

$\theta_1 = 0.4636 \ rd$ ,  $Z_1 < 0, s_2 = -1$

$X_2 = X_1 - s_1 \ 2^{-1} \ Y_1 \to X_2 = 0.8588 + 1 \times 2^{-1} \times 0 = 0.8588$

$Y_2 = Y_1 - s_1 \ 2^{-1} \ X_1 \to Y_1 = 0 - s_1 \ 2^{-1} \ X_1 = -0.4294$

$$Z_{2} = Z_{1} - s_{1} \theta_{1} \rightarrow Z_{1} = -0.262 + s_{1} 0.4636 = -0.2016$$

For  $i = 2$ ,

$$\theta_{2} = 0.2450 \ rd, \qquad Z_{2} < 0, s_{2} = -1$$

$$X_{3} = X_{2} - s_{2} 2^{-2} Y_{2} \rightarrow X_{2} = 0.8588 + 1 \times 2^{-2} \times 0.4294 = 0.75145$$

$$Y_{3} = Y_{2} + s_{2} 2^{-2} X_{2} \rightarrow Y_{3} = 0.4294 - s_{2} 2^{-2} X_{2} = 0.2147$$

$$Z_{3} = Z_{2} - s_{2} \theta_{2} \rightarrow Z_{3} = -0.2016 + s_{2} 0.2450 = -0.0434$$

and so on …, and lastly

For

$$i = 10$$

,

$\theta_{10} = 0.0020 \ rd$ ,  $Z_2 < 0, s_{10} = -1$

$X_{11} = X_{10} - s_{10} \ 2^{-10} \ Y_{10} \rightarrow X_{10} = 0.8659 + 1 \times 2^{-10} \times 0.5002 = 0.8569$

$Y_{11} = Y_{10} + s_{10} \ 2^{-10} \ X_{10} \rightarrow Y_{10} = 0.5002 - 1 \times 2^{-10} \times 0.8659 = 0.5002$

$Z_{11} = Z_{10} - s_{10} \ \theta_{10} \rightarrow Z_{10} = -0.0002 + 1 \times 0.002 = -0.002$

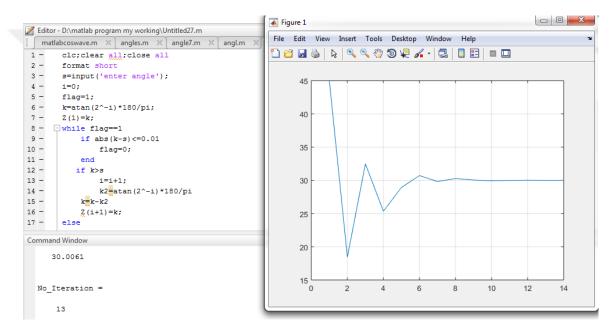

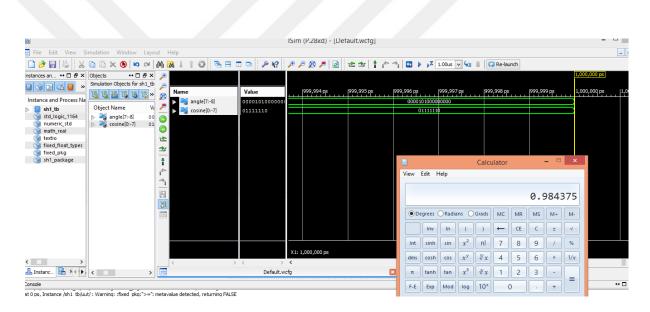

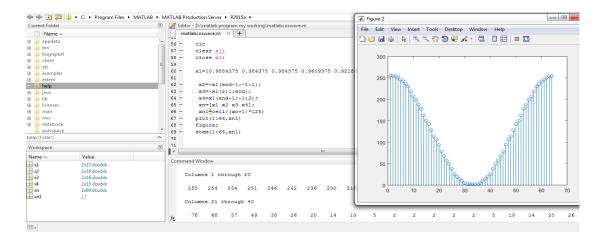

We wrote a program in MATLAB to calculate the cosine and sine values of the angles, and find the number of iterations needed considering the accuracy of the calculated value, the program and its outputs are depicted in Fig. 3.2 and Fig. 3.3.

```

clc;clear all;close all

format short

s=input('enter angle');

i=0;

flag=1;

k=atan(2^-i)*180/pi;

Z(1)=k;

while flag==1

if abs(k-s)<=0.01

flag=0;

end

if k>s

i=i+1;

```

```

k2=atan(2^-i)*180/pi

k=k-k2

Z(i+1)=k;

else

i=i+1;

k2=atan(2^-i)*180/pi

k=k+k2

Z(i+1)=k;

end

end

plot(Z)

grid on; hold on;

Iteration=i

```

Figure 3.2 Number of iterations w.r.t angles.

```

clc;clear all;close all

%epserror=[3 2 1 0.1 0.05 0.01 0.001 0.0001]

epserror=[0.0001 0.001 0.01 0.1 0.5 1 ]

z0_in=[35 14 65]

colorset={[1 0 0];[0 0 1];[0 1 0]}

colorset =cell2mat(colorset)

for k=1:3

for j=1:length(epserror)

m=0;

xi=0.607252935;

yi=0;

z0=z0 in(k);

```

```

zi=z0;

theta=[45 26.6 14 7.1 3.6 1.8 0.9 0.4 0.2 0.1]

for i=0:length(theta)

if (zi>=0)

xi1=xi-(2^-i)*yi;

yi1=yi+(2^-i)*xi;

zi1=zi-theta(i+1);

else

xi1=xi+(2^-i)*yi;

yi1=yi-(2^-i)*xi;

zi1=zi+theta(i+1);

end

xi=xi1;

yi=yi1;

zi=zi1;

m=m+1;

if (abs(zi1)<=epserror(j))</pre>

break;

end

end

itr(j)=m;

end

C=colorset(k,:);

figure(1)

plot(epserror,itr, 'color',C); xlabel('epserror'),

ylabel('iteration'),hold on;

legend('35','14','65')

pause

end

xi

cos(z0*pi/180)

yi

sin(z0*pi/180)

```

| New Open Save | Go To V Comment<br>Find V Indent<br>NAVIGATE | PUBLISH     VI       Image: Constraint of the second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second | Run and Run Sector                                              | Run and<br>Time                                                                                            |                                                    |

|---------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|               |                                              | <pre>88 - end<br/>88 - end<br/>19 - end<br/>10 - itr(j)=m;<br/>12 - end<br/>13 - C=colorset<br/>14 - figure(1)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>m % shakirsimanahmad.m (k,:); tr, 'color',C); xlabel</pre> | Figure 1<br>File Edit View Inset Tools Destop Window Help<br>File Edit View Inset Tools Destop Window Help |                                                    |

|               | •••• f:                                      | <i>t</i> >>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |                                                                                                            | Ln 1 Col 1<br>ص 12:40 هـ EN<br>۲۱/۲۱/۲۷ (۲۰۱۰ ) EN |

Figure 3.3 Iteration number w.r.t accuracy parameter.

## **CHAPTER FOUR**

#### Implementing CORDIC in FPGA using VHDL

#### **4.1. Overview of CORDIC Architectures**

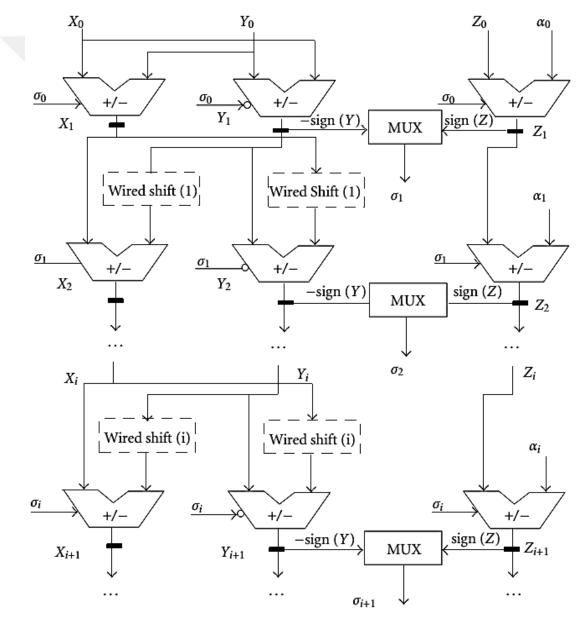

Architecture of CORDIC algorithm is presented in this section. Generally, architectures are categorized into two parts: first unfolded and second folded as depicted in Figure 9. We can have folded-architectures by implementing difference equations in hardware for CORDIC algorithm and time multiplexing of whole iterations inside a single efficient part. Folded-architectures give mechanism to an interchange zone into signal processing architectures to timing. Folded architectures has been divided to bit-serial and word-serial architectures subject to whether functional unit carry out logic into one bit or one word for every iteration of traditional CORDIC algorithm [4].

Traditionally, CORDIC algorithm can be implemented using serial bit architecture including, and entire iterations can be performed using the same hardware. In such implementations, computing device gets slow-down and, is not appropriate for high-speed application. An iterative CORDIC architecture is word serial architecture proposed in [5, 6] which is fast compared to classical implementations. Suitable simple angles  $\theta_i$  are retrieved from lookup-table.

Carry or borrow generation, addition or subtraction and variable shifting operations have degrading speed factors throughout iterations of word serial architecture, however, these operations in traditional CORDIC implementation causes the hardware to function very slowly. Thereto, through unfolding iteration process, drawbacks have been overcome by performing same iteration at each processing elements as shown in Figure 4.1. Unfolded pipelined architecture possess large throughput because of hardwired shifts instead of time and region consuming barrel shifters and removal of ROM that is main benefit of unfolded pipelined architecture over Folded architecture. Pipelined architectures give throughput enhancement by a factor of n to n-bit precision at the price of rising hardware complexity by factor not more than n.

Figure 9 Basic Architecture of CORDIC [4]

### 4.2. FPGA Implementation to CORDIC Algorithm

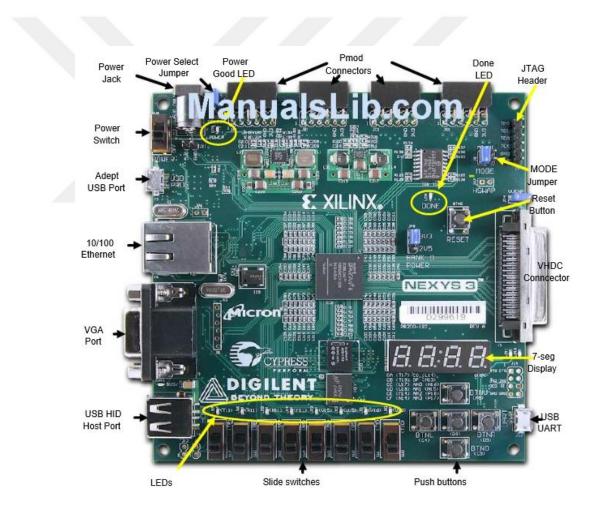

**Nexys 3<sup>TM</sup>** FPGA Board Reference is used for algorithm implementations. Nexys 3 is a complete, ready-to-utilizing digital circuit development platform involving Xilinx Spartan-6 LX16 FPGA. Spartan-6 is enhanced to high performance logic, and gives not less than 50% more capacity, improved performance, and additional resources over **Nexys 3<sup>TM</sup>** Spartan-3 500E FPGA can be found in [7].

Figure 10 Nexys 3<sup>TM</sup> FPGA Board Reference

Structures of Nexys **3<sup>TM</sup>** FPGA Board are:

- 1. 16 Mbyte Cellular RAM x16

- 2. Xilnx Sprtan-6 LX16 FPGA a 324-pin BAG package

- 3. 16 Mbyts SIP PMC non-volatile memory

- 4. 16 Mbyts parallel PCM non-volatile memory

- 5. 10/100 Ethernet PHY

- 6. On-board USB2 port to programming & data xfer

- 7. USB-UART and USB-HID port (to mouse/keyboard)

- 8. 8-bit VGA port

- 9. 100 MHz COMS oscillator

- 10. 72 I/O routed to expnsion connectors

- GIPO comprises 8 LEDs, 5 buttons,8 slide switches and 4-digit seven-segment display USB2 programming cable comprised

Besides Spartan-6 FPGA, Nexys 3 gives better group of peripherals comprising 32Mbytes of Micron's latest Phase Change Nonvolatile memory, a 10/100 Ethernet PHY, 16Mbytes of Cellular RAM, a USB-UART port, a USB host port to mice and keyboards, and an enhanced high-speed expansion connector. Large FPGA and broad set of peripherals make Nexys 3 board a perfect host to a wide variety of digital systems, comprising embedded processor designs founded on Xilinx's MicroBlaze. Nexys 3 is well-matched with every Xilinx CAD tools, comprising ChipScope, EDK, and free WebPack. Nexys 3 utilizes Digilent's latest Adept USB2 system that gives FPGA and ROM programming, automatic board tests, virtual I/O, and basic user-data transmission services.

#### **CHAPTER FIVE**

**Generation of Sinusoidal Signals**

In order to generate an output signal having a sinusoidal waveform, we will be use a digital stores at different locations binary-coded amplitudes at equally spaced instants of time during a complete cycle of a sine wave. Those locations are addressed in turn by incomes of a pulse counter and the signals supplied by the memory are passed to a digital/analogue converter from which the required output signal is resultant. The pulse signal supplied to the counter is achieved from a sequence of clock pulses by a programmable divider. To get a frequency change in the output signal (for the purpose of signaling binary data), the frequency of the divider is changed in a sequence of steps so that the overall change in output frequency is less quick than would otherwise be the case.

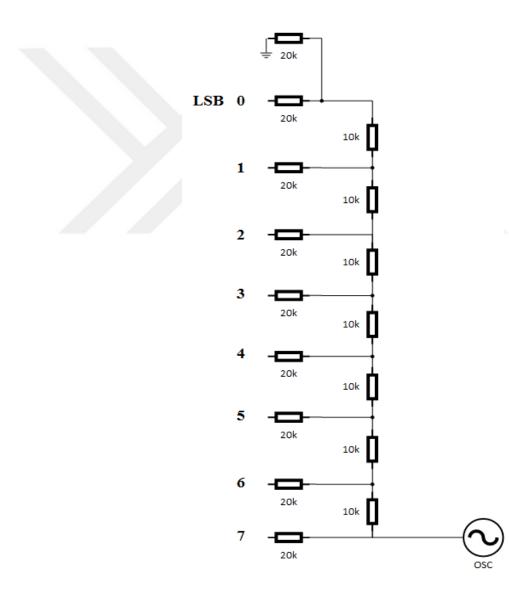

#### 5.1. Digital to analog Converter

The abbreviation DAC is refers to converts from digital to analog. A device gives an analogue signal from convert's digital data. The digital to analogue converter takes serial numbers of discrete values as input values and gives an analogue signal that is instantaneous with the equivalent numerical value. Several kinds of Digital to Analog converter ICs are obtainable commercially built on this same standard. The R-2R ladder

circuit is constructed by a set of resistors of two values. It makes the circuit simpler and economical for several applications.

R-2R biased resistor ladder circuit consumptions only 2 set of resistors- R and 2R. If you need to construct a very fixed DAC, be accurate while selecting the values of resistors that will exactly equal to the R-2R ratio

Figure 11 Digital to Analog Converter

#### **Simulation and Result**

#### 5.2. Introduction

In order to test a circuit by software we can use simulator platforms. Conventionally, we can build a digital circuit on board using chips to test logical circuit but this state has some disadvantages. One of the important disadvantages is high cost, because in this method we need heavy expensive lab equipment and hardware. Cost can increase more because many chips may be hooked up and incorrectly destroyed. Some errors often difficult to detect on board. Solution to these problems is design re-usable circuits. In next step, we will explain Xilinx ISE Design Suite 14.5 ISim Simulator.

We will learn the following topics:

- 1. How to use a simulator and learn different capabilities of it?

- 2. How to create a test bench in (VHDL) in order to be used by simulator?

- 3. How to verify functionality (CORDIC Algorithm) by using Xilinx ISim Simulator?

#### 5.2.1. Getting Started

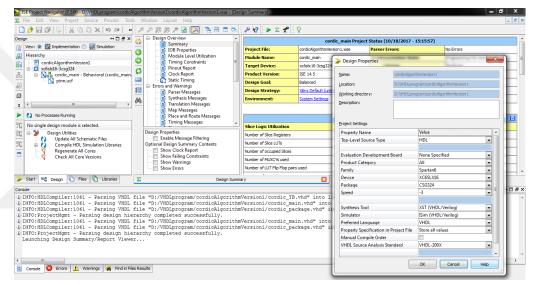

In this section, we will describe requirements to conducting behavioral simulations. To create design files in VHDL, we open icon (file) and chose open (new project) option and name it, see Fig. 12.

- To simulate design, we need a bench file to provide stimulus to design.

- Simulation Libraries: We need Xilinx simulation libraries when we use Xilinx primitive or IP core in design.

| >                                                                               | ISE Project Navigator (P.28xd)                                                     | - 🗆 🗙 |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|

| File Edit View Project Source Process Tools Window Layout Help                  |                                                                                    |       |

| Start ↔ □ 🗗 X                                                                   | New Project Wizard                                                                 |       |

| Welcome to the ISE® Design Suite Project commands                               | © Treate New Project<br>Specify project location and type.                         |       |

| Open Project Project Browser New Project Open Example                           | Enter a name, locations, and comment for the project Name: cordicAlgorithmversion1 |       |

| Recent projects Double click on a project in the list below to open             | Location: D:\ISE_projects\cordicAlgorithmversion1                                  |       |

| Additional resources Tutorials on the Web Desion Resources Additional resources | Working Directory: D:\USE_projects\cordcAlgorithmversion1                          |       |

|                                                                                 | Select the type of top-level source for the project<br>Top-level source type:      |       |

|                                                                                 | HOL                                                                                |       |

|                                                                                 | More Info Next > Cancel                                                            |       |

| Errors                                                                          |                                                                                    | +□6   |

Figure 12 How to create a design file.

# 5.3. Behavioral Simulation Using ISim

The steps to be followed to simulate your design are:

- 1. Open your design project (cordicAlgorithversion1).

- 2. Choose simulation mode.

- 3. Add a HDL test bench to your existing design.

- 4. Identify simulations.

- 5. Determine simulation properties.

- 6. Simulation performance.

- 7. Add signals.

8. Signal analysis.

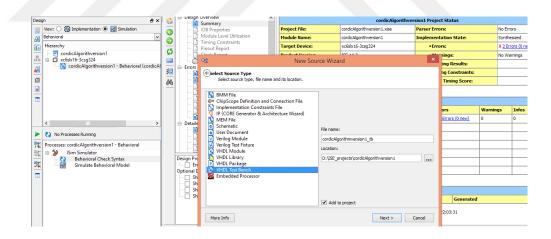

### 5.3.1. How to open project

- 1. Open Project Navigator from all programs Xilinx ISE design suite 14.5.

- 2. We see project navigator window Figure 13.

- 3. We have two method to open any project:

1. Directly open project and chose project from list.

2. Open existing project on screen and we will see previous project to example (cordicAlgorithversion1) and chose it.

Figure 13. Project navigator window

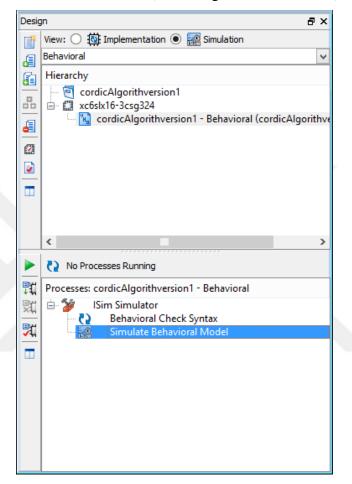

4. We see two choices, implementation or simulation, See Fig. 14.

| > 19  | SE Pro | ject I     | Vavigato | or (P.58f) - | D:\VHDLp | program\cc | ordicAlg     | orithmVersi | on1\cord | icAlgorit | hmVersio | n1.xise | - [Desi | gn Sun | nmary] |   |          |            |

|-------|--------|------------|----------|--------------|----------|------------|--------------|-------------|----------|-----------|----------|---------|---------|--------|--------|---|----------|------------|

| ∑ F   | ile    | Edit       | View     | Project      | Source   | Process    | Tools        | Window      | Layout   | Help      |          |         |         |        |        |   |          |            |

|       | 9      |            | 18       | 1 X C        | n là X   | 50         | »            | PPB         | ) Ø /    | 2         | N 🔁 I    | = =     | Ð       | ۶ 🔑    | ? 🕨    | Σ | <b>*</b> | 2          |

| Desig | n      | _          | _        | _            | _        | -          | _            |             |          |           |          |         |         |        |        | ↔ | □∂×      | <u></u>    |

| 1     | V ew:  | $\bigcirc$ | 🔯 Imple  | mentation    | 💿 🔝 Sir  | mulation   | $\mathbf{>}$ |             |          |           |          |         |         |        |        |   |          | -          |

| a     | Behav  | iorai      |          |              | _        | -          |              |             |          |           |          |         |         |        |        |   | -        | $\bigcirc$ |

|       | Hiera  | archy      |          |              |          |            |              |             |          |           |          |         |         |        |        |   |          | $\odot$    |

|       |        | e co       | rdicAlg  | orithmVers   | ion1     |            |              |             |          |           |          |         |         |        |        |   |          | Ç5         |

| 00    | ė- 6   |            | 5slx16-3 |              |          |            |              |             |          |           |          |         |         |        |        |   |          | HIRE       |

| 4     | G      | ÷ "H       | cordic   | _main_tb ·   | bench (c | ordic_TB.v | hd)          |             |          |           |          |         |         |        |        |   |          | _          |

|       |        |            |          |              |          |            |              |             |          |           |          |         |         |        |        |   |          | 38         |

|       |        |            |          |              |          |            |              |             |          |           |          |         |         |        |        |   |          | A          |

| 1     |        |            |          |              |          |            |              |             |          |           |          |         |         |        |        |   |          | -          |

| -     |        |            |          |              |          |            |              |             |          |           |          |         |         |        |        |   |          | -          |

| ш     |        |            |          |              |          |            |              |             |          |           |          |         |         |        |        |   |          | -          |

Figure 14 Explanation of the choices for the implementation and simulation options

5. You should use implementation mode when you want to design a circuit using VHDL. On other hand, you should switch to simulation mode when you want to

simulate your design. To simulate the design, we should use Simulation mode and chose implementation mode when you want to design a circuit using VHDL.

•When we use simulation mode, we see behavioral check syntax and simulate behavioral model, translate simulation (that is executed after synthesis), mapping (that is implemented after executing design), route simulation (that is achieved after mapping, placement and routing).

#### 5.4. How to add an HDL Test Bench

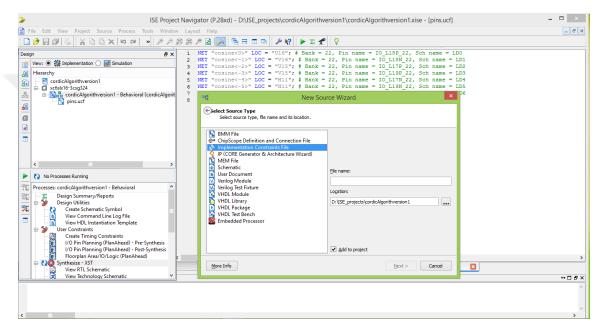

In order to create a new test bench file to our project and modify by editing it with statements, we should follow these steps:

1. Highlight our project and then click on new source and select VHDL Test Bench and enter "cordicAlgorithversion1\_tb", and click next, see Fig. 15.

Figure 15. Creating a test bench.

|         |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xise - [Design Summary] |          |                                                                             |           |                                                       |                                           | X<br>8 × |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|-----------------------------------------------------------------------------|-----------|-------------------------------------------------------|-------------------------------------------|----------|

|         | Design<br>Wex: Diffunction (Constraints)<br>Behaviore                                                                                                                                                 | 이 에 🕨 🥬 위 및 위 🗟 💌 😤 🗏                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |          | Summary<br>IOB Properties<br>Module Level Utilization                       | Project d | 15:15:57)<br>ordicAlgo Parser Er                      | (10/18/2017 -                             | Î        |

|         | Hierachy<br>cordicAlgorithmVersion1<br>CordicAlgorithmVersion1<br>CordicAlgorithmVersion1<br>CordicAlgorithmVersion1<br>CordicAlgorithmVersion1<br>CordicAlgorithmVersion1<br>CordicAlgorithmVersion1 | 7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | <b>G</b> | Pinout Report<br>Clock Report E<br>Static Timing<br>d Warnings              |           |                                                       | ng File                                   |          |

| /       |                                                                                                                                                                                                       | New Source Wizard  Select Source Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |          | arser Messages<br>ynthesis Messages<br>ranslation Messages<br>Jap Messages  | Device:   | ksg324                                                | arnings 4.<br>Warnings                    | -        |

|         | No Processes Running     No single design module is selected.                                                                                                                                         | Select source type, file name and its location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |          | iming Messages<br>litgen Messages<br>III Implementation Messages<br>Reports | Goat      | R                                                     | sults: Al Signals<br>Complete<br>y Routed | e        |

| To save | 14 No single design module is selected.<br>했 ④ 梦 Design Utilities                                                                                                                                     | <ul> <li>IP (CORE Generator &amp; Architecture Wizard)</li> <li>MEM File</li> <li>Schematic</li> <li>User Document</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | File name:              |          | erties<br>le Message Filtering<br>ign Summary Contents                      | Strategy: | efault Co<br>unlocked) nt<br>wstem Fin<br>lettings Th | nstrai<br>s: 0 (Timing<br>ming Report)    | ĩ        |

| all     |                                                                                                                                                                                                       | Basic Process Tools Window Dupont Help       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview       Image: Second Design Overview         Image: Second Design Overview <td< th=""><th>e</th></td<> | e                       |          |                                                                             |           |                                                       |                                           |          |