# OFDM TRANSMITTER AND RECEIVER IMPLEMENTATION ON FPGA

SAMET TİLKİOĞLU

**JUNE 2018**

## ÇANKAYA UNIVERSITY

# GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

## ELECTRONIC AND COMMUNICATION ENGINEERING

MASTER THESIS

OFDM Transmitter and Receiver Implementation on FPGA

BY

SAMET TİLKİOĞLU

JUNE 2018

Title of the Thesis: OFDM Transmitter and Receiver Implementation on FPGA.

Submitted by Samet TİLKİOĞLU

Approval of the Graduate School of Natural and Applied Sciences, Çankaya University.

Prof. Dr. Can COC Director

I certify that this thesis satisfies all the requirements as a thesis for the degree of Master of Science.

Asst. Prof. Dr. Özgür ERGÜL Deputy Chairman of Deparment

This is to certify that we have read this thesis and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

Prof. Dr. Halil Tanyer EYYUBOGLU Supervisor

Examination Date: 08.06.2018

**Examining Committee Members**

Prof. Dr. Halil Tanyer EYYUBOGLU

Assoc. Prof. Dr. Hüsnü Deniz BAŞDEMİR

Assist. Prof. Dr. Javad RAHEBI

(Çankaya Uni.)

(Çankaya Uni.)

(Türk Hava Kurumu Uni.)

### STATEMENT OF NON-PLAGIARISM PAGE

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results fully cited and referenced all material and results that are not original to this work.

Name, Last Name

: Samet TİLKİOĞLU

Signature

Date

: LAM

: 08.06.2018

¥

### ABSTRACT

#### **OFDM Transmitter and Receiver Implementation FPGA**

TİLKİOĞLU, Samet

M.Sc. Department of Electronic and Communication Engineering

Supervisor: Prof. Dr. Halil Tanyer EYYUBOGLU

June 2018, 84 pages

In this thesis, digital modulations which are 4QAM and QPSK are designed and implemented using FPGA hardware using OFDM communication technique. The Genesys Virtex-5 development card produced by Digilent is used as hardware. The development of the relevant card software was developed with the System Generator Blocks and native Simulink blocks in Simulink (MATLAB 2012a) and transferred to the corresponding card. In the steps of developing algorithms, digital modulation techniques are used.

**Keywords:** OFDM (Orthogonal Frequency-Division Multiplexing), Transmitter, Receiver, Wireless Communication, FPGA (Field Programmable Gate Array), MATLAB, Simulink, System Generator, FFT, IFFT

### ÖΖ

#### FPGA üzerinde OFDM Alıcı ve Verici Uygulaması

TİLKİOĞLU, Samet

Yüksek Lisans, Elektronik ve Haberleşme Mühendisliği Anabilim Dalı

Tez Yöneticisi: Prof. Dr. Halil Tanyer EYYUBOGLU

Haziran 2018, 84 sayfa

Bu tezde, OFDM haberleşme tekniği kullanılarak dijital modülasyonlardan olan 4QAM ve QPSK modülasyon çeşitleri, FPGA donanımı kullanılarak tasarlanmış ve gerçekleştirilmiştir. Donanım olarak Digilent firması tarafından üretilen Genesys Virtex-5 geliştirme kartı kullanılmıştır. İlgili kartın yazılımının geliştirilmesi, Simulink (MATLAB 2012a) üzerinde System Generator Blokları ve Simulink Blokları kullanılarak geliştirilmiş ve ilgili karta aktarılmıştır. Algoritma geliştirme safhalarında, dijital modülasyon teknikleri kullanılmıştır.

Anahtar Kelimeler: OFDM (Ortogonal Frekans Bölmeli Çoğullama), Verici, Alıcı, Kablosuz Haberleşme, FPGA(Alanda Programlanabilir Kapı Dizileri), MATLAB, Simulink, Xilinx ISE, System Generator, FFT, IFFT

#### ACKNOWLEDGEMENT

At the end of my thesis, I am thankful to all those people who supports and motivates me until this time.

First of all, I would like to thank to my supervisor Prof. Dr. Halil Tanyer EYYUBOGLU for his help and selfless support with both theoretical and practical. I am very thankful for his supervision and guidance to accomplish the correct ending during my education and M.Sc. thesis duration.

And also, I want to thank to Çankaya University Department of Electronic and Communication Engineering Members who supported me since the beginning of undergraduate education.

Finally, I take this opportunity to express the great gratitude to my family. I return thanks to my family for their absolute supports and encouragements to my life.

# TABLE OF CONTENT

| STATEMEN    | T OF NON-PLAGIARISM PAGEiii                              |

|-------------|----------------------------------------------------------|

| ABSTRACT    | iv                                                       |

| ÖZ          | v                                                        |

| ACKNOWL     | EDGEMENTvi                                               |

| TABLE OF    | CONTENTvii                                               |

| LIST OF TA  | BLESx                                                    |

| LIST OF FIG | GURESxi                                                  |

| LIST OF AB  | BREVIATIONxv                                             |

| LIST OF SY  | MBOLSxvii                                                |

| CHAPTER 1   | . INTRODUCTION1                                          |

| 1.1.        | Background1                                              |

|             | 1.1.1. Orthogonal Frequency Division Multiplexing (OFDM) |

|             | Basics1                                                  |

|             | 1.1.2. Field Programmable Gate Array (FPGA) Basics       |

| 1.2.        | Thesis Overview                                          |

| CHAPTER 2   | 2. WIRELESS COMMUNICATION AND DIGITAL                    |

| MODULATI    | ON TYPES                                                 |

| 2.1.        | An Overview of Wireless Communications7                  |

| 2.2.        | Digital Modulation Types8                                |

|             | 2.2.1. ASK (Amplitude Shift Keying)9                     |

|             | 2.2.2. FSK (Frequency Shift Keying)10                    |

|             | 2.2.3. PSK (Phase Shift Keying)10                        |

|             | 2.2.4. QAM (Quadrature Amplitude Modulation)11           |

| CHAPTER 3   | <b>ORTHOGONAL FREQUENCY DOMAIN</b>                       |

| MULTIPLE    | XING (OFDM)                                              |

| 3.1.        | Expression of OFDM13                                     |

| 3.2.        | Orthogonality                                            |

| 3.3.     | Concep   | t of FFT and I  | FFT                               |          |

|----------|----------|-----------------|-----------------------------------|----------|

|          | 3.3.1.   | Discrete Four   | ier Transform (DFT)               |          |

|          | 3.3.2.   | Inverse Discre  | ete Fourier Transform (IDFT)      | 21       |

| 3.4.     | Serial t | o Parallel Con  | version                           |          |

| 3.5.     | Paralle  | to Serial Con   | version                           |          |

| 3.6.     | Guard    | Interval / Cycl | ic Prefix                         |          |

| 3.7.     | Cyclic   | uffix           |                                   |          |

| 3.8.     | Window   | ving            |                                   |          |

| 3.9.     | Channe   | l Models        |                                   |          |

|          | 3.9.1.   | Additive Whit   | te Gaussian Noise (AWGN)          |          |

|          | 3.9.2.   | Multipath Fac   | ding                              |          |

|          |          | 3.9.2.1. Rayl   | eigh Fading                       |          |

|          |          | 3.9.2.2. Ricia  | an Fading                         |          |

| 3.10.    |          | Performance     | of OFDM System                    |          |

|          | 3.10.1.  | Bit Error Ra    | te (BER) Measurement              |          |

|          | 3.10.2.  | Signal to Nois  | se Ratio (SNR)                    |          |

| CHAPTER  | 4.       | FPGAs & DIO     | GILIENT'S GENESYS VIRTEX-5        |          |

| DEVELOPI | LMENT    | BOARD           |                                   |          |

| 4.1.     | Digilen  | Genesys™ Vi     | irtex-5 FPGA Development Board    |          |

| 4.2.     | Digilen  | Genesys™ Vi     | irtex-5 FPGA Development Board Fe | ature.34 |

| 4.3.     | Board    | Configuration.  |                                   |          |

| 4.4.     | Adept    | ystem           |                                   |          |

| CHAPTER  | 5.       | MATHWORI        | KS' MATLAB/SIMULINK AND XII       | JNX'S    |

| SYSTEM G | ENERA    | FOR FOR DS      | Р                                 |          |

| 5.1.     | MathW    | orks' MATLA     | B/Simulink                        |          |

| 5.2.     | Xilinx I | SE Design Sui   | te and System Generator           |          |

| 5.3.     | MATL     | AB/Simulink &   | & System Generator Configuration  | 41       |

| 5.4.     | Xilinx I | locksets        |                                   |          |

|          | 5.4.1.   | Organization    | of Blockset Libraries             | 42       |

|          | 5.4.2.   | Used Xilinx S   | ystem Generator Blocks            | 44       |

|          | 5.4.3.   | Used Simulinl   | k Blocks                          | 51       |

|          | 5.4.4.   | Conversion of   | f Simulink Model for Target Board |          |

| CHAPTER  | 6.      | DESIGN and IMPLEMENTATION of OFDM                   |

|----------|---------|-----------------------------------------------------|

| RECEIVER | R AND T | FRANSMITTER ON GENESYS VIRTEX-5 FPGA                |

| DEVELOP  | MENT    | BOARD                                               |

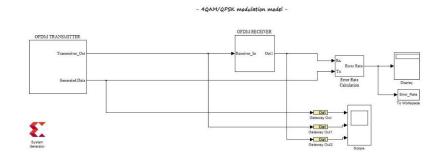

| 6.1.     | QPSK    | / 4QAM Modulation Simulink Model 57                 |

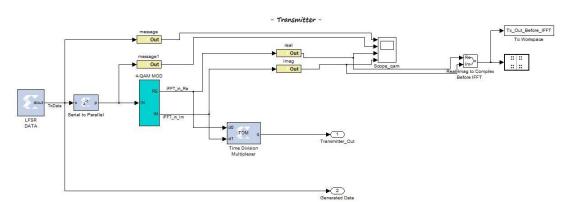

|          | 6.1.1.  | QPSK / 4QAM Modulation Simulink Model – Transmitter |

|          | Side    |                                                     |

|          | 6.1.2.  | QPSK / 4QAM Modulation Simulink Model – Receiver    |

|          | Side    |                                                     |

|          | 6.1.3.  | QPSK / 4QAM Modulation Simulink Model – Channel 63  |

|          | 6.1.4.  | QPSK / 4QAM Modulation Simulink Model – Error Rate  |

|          | Calcul  | ation 66                                            |

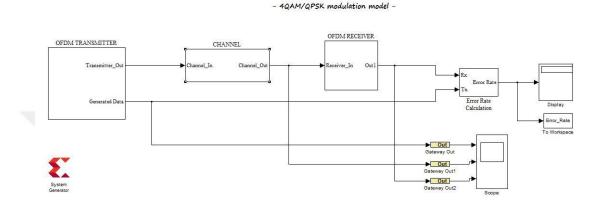

| 6.2.     | OFDM    | I System using 4QAM Modulation Simulink Model67     |

|          | 6.2.1.  | OFDM System using 4QAM Modulation Simulink Model –  |

|          | Trans   | mitter Side                                         |

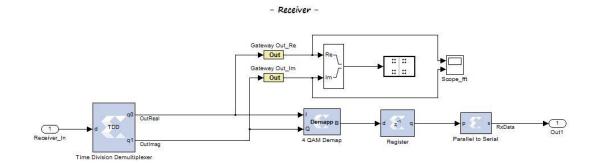

|          | 6.2.2.  | OFDM System using 4QAM Modulation Simulink Model -  |

|          | Receiv  | er Side72                                           |

|          | 6.2.3.  | OFDM System using 4QAM Modulation Simulink Model -  |

|          | Chann   | rel                                                 |

|          | 6.2.4.  | OFDM System using 4QAM Modulation Simulink Model –  |

|          | Error   | Rate Calculation76                                  |

| CHAPTER  | 7.      | CONCLUSION                                          |

| REFEREN  | CES     |                                                     |

| APPENDIX | ζ       |                                                     |

# LIST OF TABLES

| Table 1: Organization of Blockset Libraries of Xilinx [52] | . 43 |

|------------------------------------------------------------|------|

| Table 2: ROM Block Settings for QAM                        | . 59 |

| Table 3: ROM Block Settings for QPSK                       | . 59 |

| Table 4: Mcode Block's Code for QAM Demapper               | . 62 |

## LIST OF FIGURES

| Figure 1: Transistor-Based Technology Timeline [26]                              | 4    |

|----------------------------------------------------------------------------------|------|

| Figure 2: FPGA Design Flow [29]                                                  | 5    |

| Figure 3: Basic Digital Communication Model                                      | 8    |

| Figure 4: Digital Modulation Types                                               | 9    |

| Figure 5: ASK modulation for Digital Data                                        | 9    |

| Figure 6: ASK, BFSK and BPSK Modulation Types[34]                                |      |

| Figure 7: QPSK                                                                   | . 11 |

| Figure 8: QAM Modulator [34]                                                     | . 11 |

| Figure 9: Commonly used QAM (Quadrature Amplitude Modulation) Constellation      | ns   |

| [35]                                                                             | . 12 |

| Figure 10: Signal Constellations of Some Basic Single-Carrier Digital Modulation |      |

| Techniques a) Binary-ASK b) Binary-PSK c) QPSK d) 8PSK                           | .12  |

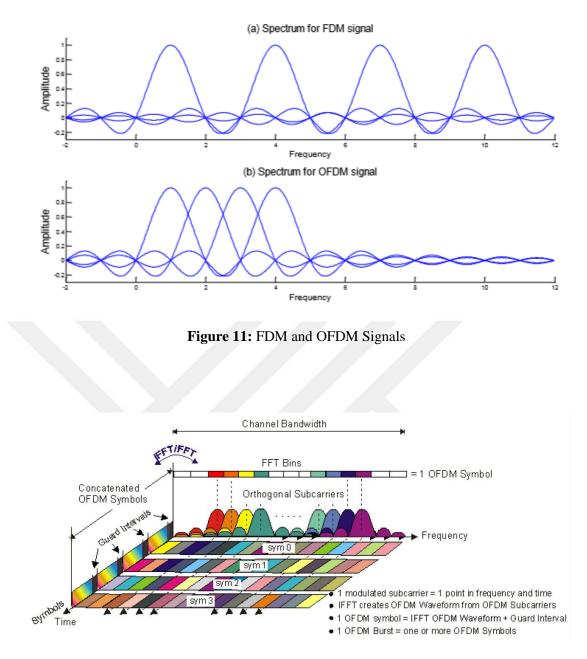

| Figure 11: FDM and OFDM Signals                                                  | . 14 |

| Figure 12: Frequency-Time Representative of an OFDM Signal [36]                  | . 14 |

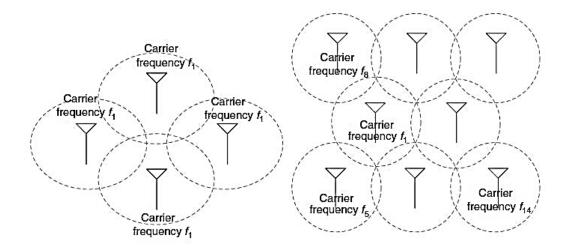

| Figure 13: Single-Frequency and Multi-Frequency Network [32]                     | .15  |

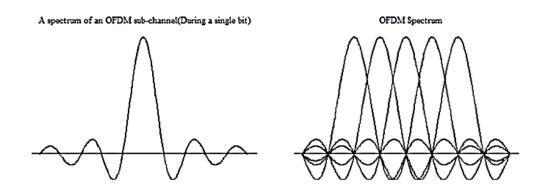

| Figure 14: OFDM Spectrum [38]                                                    | .15  |

| Figure 15: System Parameters of Several Wireless Communication Standards using   | g    |

| the OFDM Technology                                                              | . 16 |

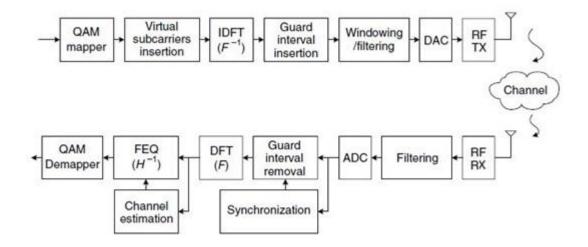

| Figure 16: OFDM Transceiver Architecture for QAM [32]                            | . 17 |

| Figure 17: FFT Algorithm for Parallel Data                                       | . 20 |

| Figure 18: Simulink FFT Block                                                    | 21   |

| Figure 19: Simulink IFFT Block                                                   | . 22 |

| Figure 20: IFFT in Transmitter Side and FFT in Receiver Side                     | . 22 |

| Figure 21: Serial to Parallel Conversion                                         | . 22 |

| Figure 22: Parallel to Serial Conversion                                         | .23  |

| Figure 23: OFDM Symbol with Cyclic Prefix                                        | .23  |

| Figure 24: Time / Frequency Domain Description of OFDM Symbols with O                    | - |

|------------------------------------------------------------------------------------------|---|

| Prefix<br>Figure 25: (a) Illustration of ISI due to multipath delay; (b) zero-padding gu |   |

| interval to avoid ISI; (c) guard interval with cyclic prefix to eliminate ISI an         |   |

| [32]                                                                                     |   |

| Figure 26: OFDM symbol with both Cyclic Prefix (CP) and Cyclic Suffix (                  |   |

| Figure 27: Cyclic Extension and Windowing of the OFDM Symbol                             |   |

| Figure 28: Multipath Fading 1                                                            |   |

| Figure 29: Multipath Fading 2                                                            |   |

| Figure 30: Multipath Propagation Effects                                                 |   |

| Figure 31: Fading Effect                                                                 |   |

| Figure 32: Phasor Diagram of Rician Fading                                               |   |

| Figure 33: Simulink Error Rate Calculation Block                                         |   |

| Figure 34: Theoretical Bit Error Probability vs. <i>Eb/N0</i> for M-QAM-N                |   |

| Figure 35: Digilent's Genesys Virtex-5 FPGA Development Board                            |   |

| Figure 36: Board Programming Configuration                                               |   |

| Figure 37: Adept Screen before Connection is Established                                 |   |

| Figure 38: Adept Screen after Connection is Established                                  |   |

| Figure 39: Adept Test Window                                                             |   |

| Figure 40: MATLAB - Simulink and Its Blockset Screen                                     |   |

| Figure 41: Xilinx ISE Design Suite Installation Screen                                   |   |

| Figure 42: Simulink System Generator Blocksets [47]                                      |   |

| Figure 43: MATLAB Configuration Window of System Generator                               |   |

| Figure 44: Xilinx System Generator - Constant Block Symbol                               |   |

| Figure 45: Xilinx System Generator - Convert Block Symbol                                |   |

| Figure 46: Xilinx System Generator - Counter Block Symbol                                |   |

| Figure 47: Xilinx System Generator - Delay Block Symbol                                  |   |

| Figure 48: Xilinx System Generator - Down Sample Block Symbol                            |   |

| Figure 49: Xilinx System Generator - Gateway In Block Symbol                             |   |

| Figure 50: Xilinx System Generator - Gateway Out Block Symbol                            |   |

| Figure 51: Xilinx System Generator - LFSR Block Symbol                                   |   |

| Figure 52: Xilinx System Generator - Serial to Parallel Block Symbol                     |   |

| Figure 53: Xilinx System Generator - Parallel to Serial Block Symbol                     |   |

| Figure 54: Xilinx System Generator – Register Block Symbol                    | . 47 |

|-------------------------------------------------------------------------------|------|

| Figure 55: Xilinx System Generator Block Symbol                               | . 47 |

| Figure 56: Xilinx System Generator - Time Division Demultiplexer Block Symbol | 147  |

| Figure 57: Xilinx System Generator - Time Division Multiplexer Block Symbol   | . 48 |

| Figure 58: Xilinx System Generator - Up Sample Block Symbol                   | . 48 |

| Figure 59: Xilinx System Generator - Mcode Block Symbol                       | . 48 |

| Figure 60: Xilinx System Generator - ROM Block Symbol                         | . 49 |

| Figure 61: Xilinx System Generator - Fast Fourier Transform 7.1 Block Symbol  | . 49 |

| Figure 62: Xilinx System Generator - AddSub Block Symbol                      | . 49 |

| Figure 63: Xilinx System Generator - Cmult Block Symbol                       | . 50 |

| Figure 64: Xilinx System Generator - Delay Block Symbol                       | . 50 |

| Figure 65: Xilinx System Generator - Mult Block Symbol                        | . 50 |

| Figure 66: Xilinx System Generator - WaveScope Block Symbol                   | . 51 |

| Figure 67: Simulink - Terminator Block Symbol                                 | . 51 |

| Figure 68: Simulink - Inport Block Symbol                                     | . 51 |

| Figure 69: Simulink - Outport Block Symbol                                    | . 51 |

| Figure 70: Simulink - Scope and Floating Scope Block Symbol                   | . 52 |

| Figure 71: Simulink - Real-Imag to Complex Block Symbol                       | . 52 |

| Figure 72: Simulink - To Workspace Block Symbol                               | . 52 |

| Figure 73: Simulink - Discrete Time Scatter Plot Scope Block Symbol           | . 52 |

| Figure 74: Simulink - Error Rate Calculation Block Symbol                     | . 53 |

| Figure 75: Simulink - Display Block Symbol                                    | . 53 |

| Figure 76: System Generator Icon                                              | . 53 |

| Figure 77: System Generator Configuration Window                              | . 54 |

| Figure 78: System Generator Board Description Builder Window                  | . 54 |

| Figure 79: Adding Target FPGA Window                                          | . 55 |

| Figure 80: 4QAM & QPSK Modulation Simulink Model without Channel              | . 57 |

| Figure 81: 4QAM & QPSK Modulation Simulink Model – Transmitter Subsystem      | 57   |

| Figure 82: Setting Window Xilinx Serial to Parallel Block                     | . 58 |

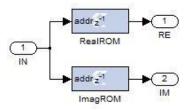

| Figure 83: 4-QAM Mapping Subsystem                                            | . 58 |

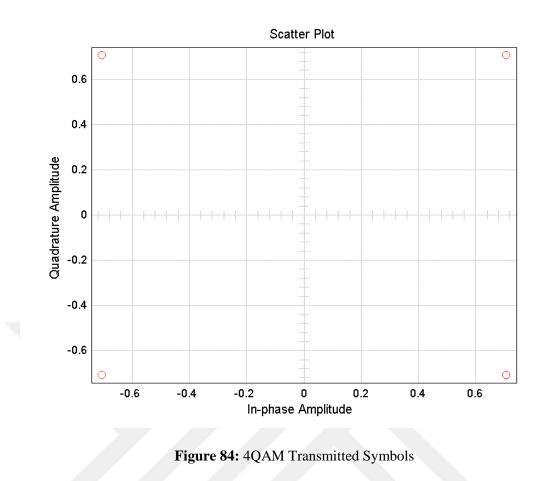

| Figure 84: 4QAM Transmitted Symbols                                           | . 60 |

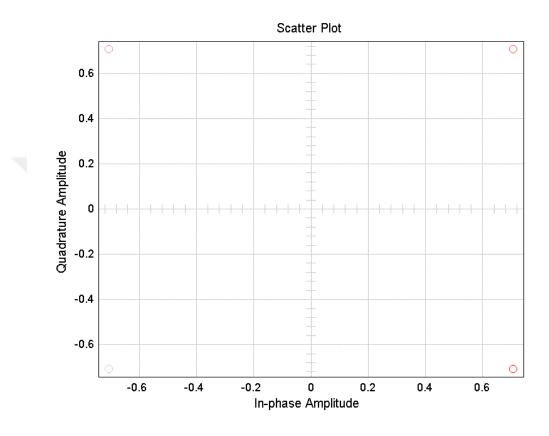

| Figure 85: 4QAM & QPSK Modulation Simulink Model – Receiver Subsystem         | . 60 |

| Figure 86: 4QAM Received Symbols                                              | . 61 |

| Figure 87: Generated & Received Datas of Model for 4-QAM Modulation (from        |      |

|----------------------------------------------------------------------------------|------|

| Scope and Floating Scope block)                                                  | . 62 |

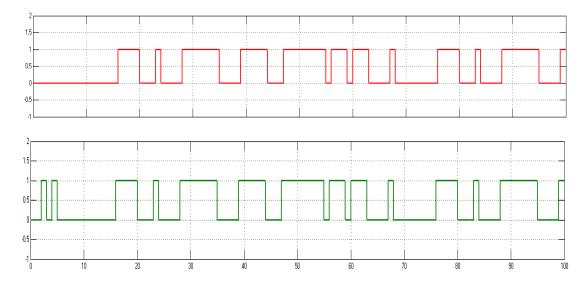

| Figure 88: 4QAM & QPSK Modulation Simulink Model with Channel                    | . 63 |

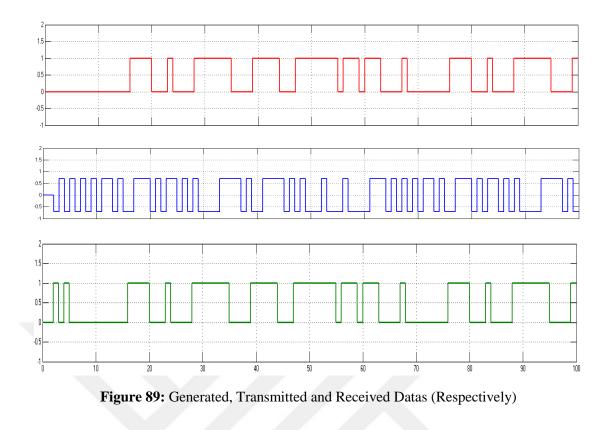

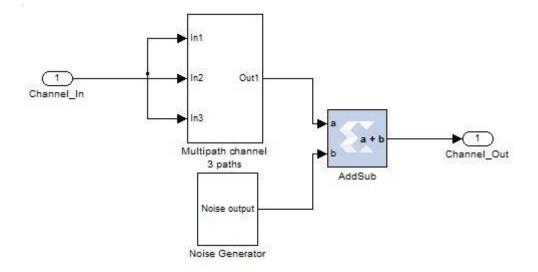

| Figure 89: Generated, Transmitted and Received Datas (Respectively)              | . 64 |

| Figure 90: Channel Subsystem                                                     | . 64 |

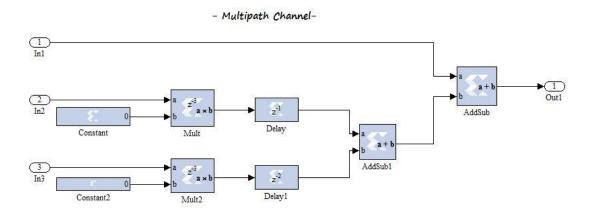

| Figure 91: Multipath Fading Subsystem                                            | . 65 |

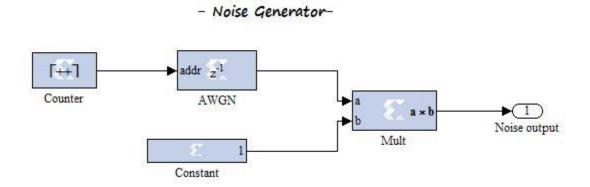

| Figure 92: Additive White Gaussian Noise Generator Subsystem                     | . 65 |

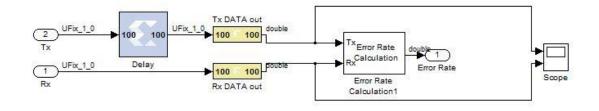

| Figure 93: Error Rate Calculation Subsystem of Model                             | . 66 |

| Figure 94: Generated & Received Datas of Model for 4-QAM Modulation (from        |      |

| Scope and Floating Scope block)                                                  | . 67 |

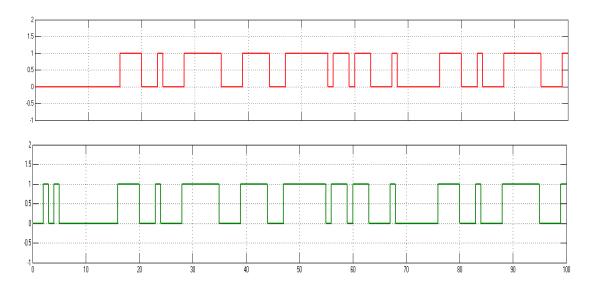

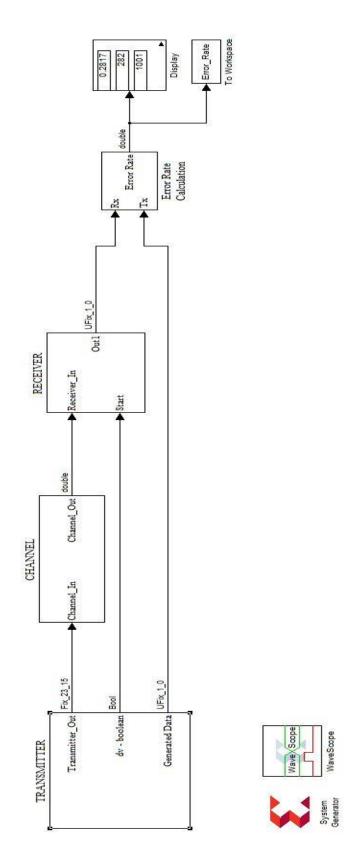

| Figure 95: Simulink Model of Implementation                                      | . 68 |

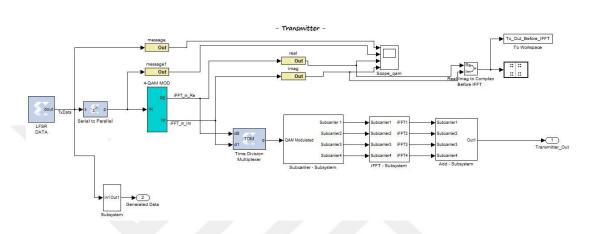

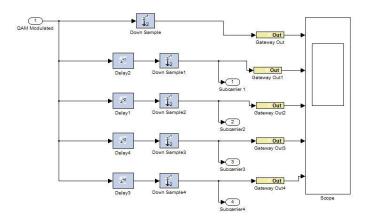

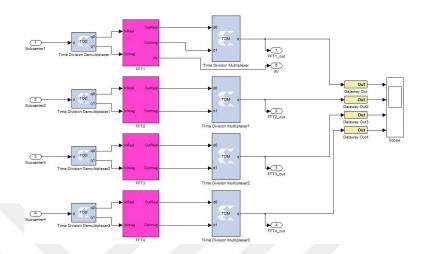

| Figure 96: OFDM System - Transmitter Subsystem of Model                          | . 69 |

| Figure 97: : OFDM System - Transmitter Side - Dividing into Subcarriers Subsyste |      |

|                                                                                  | . 69 |

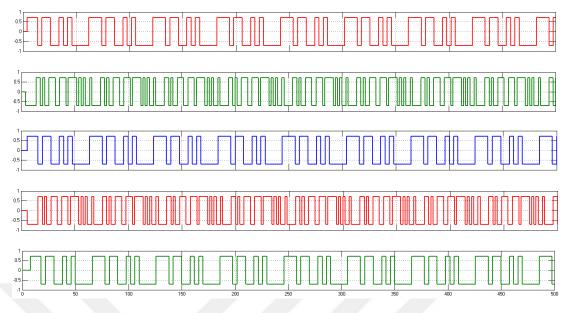

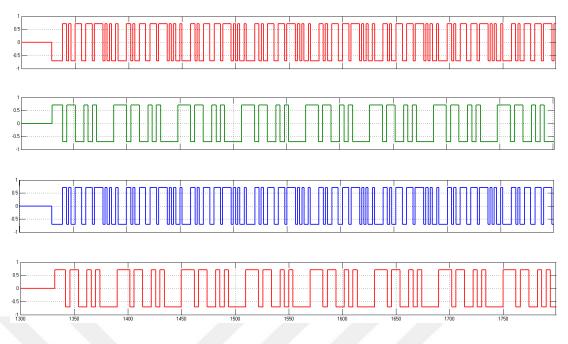

| Figure 98: Generated Data & Subcarriers (respectively)                           | . 70 |

| Figure 99: OFDM System – Tranmitter Side – Applying IFFT to all of Subcarriers   | ;    |

| Subsystem                                                                        | .71  |

| Figure 100: Results of Applying IFFT to all of Subcarriers (after Time Division  |      |

| Multiplexer Block)                                                               | .71  |

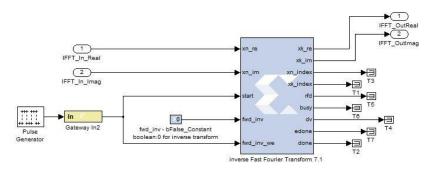

| Figure 101: OFDM System – Transmitter Side – IFFT Subsystem                      | . 72 |

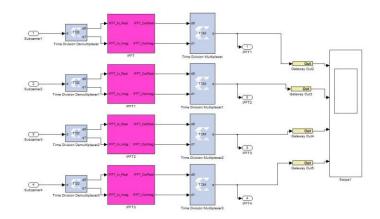

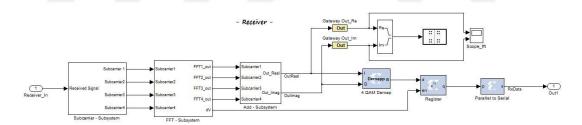

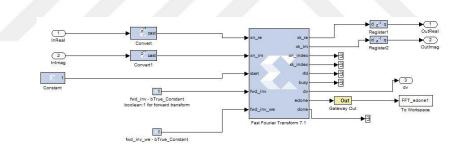

| Figure 102: OFDM System – Receiver Subsystem                                     | . 72 |

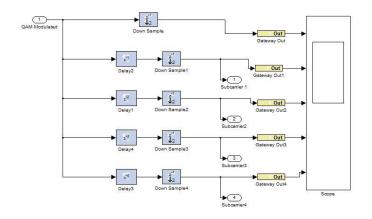

| Figure 103: OFDM System – Receiver Side – Dividing into Subcarriers Subsystem    | n    |

|                                                                                  | .73  |

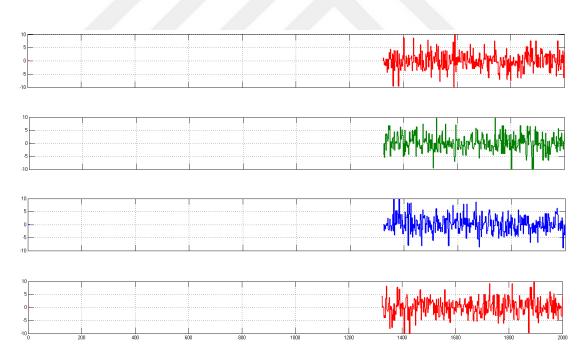

| Figure 104: Results of Dividing into Subcarriers                                 | .73  |

| Figure 105: OFDM System – Receiver Side – Applying FFT to all of Subcarriers     |      |

| Subsystem                                                                        | . 74 |

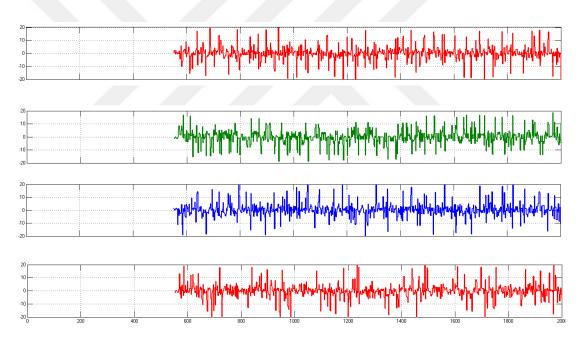

| Figure 106: Results of Multiplexed FFT Results                                   | . 75 |

| Figure 107: OFDM System – Receiver Side – FFT Subsystem                          | .75  |

## LIST OF ABBREVIATION

| Abbreviation | Definition                                        |

|--------------|---------------------------------------------------|

| <b>3</b> G   | Third Generations                                 |

| 3GPP         | Third Generation Partnership Project              |

| <b>4</b> G   | Fourth Generations                                |

| ADSL         | Asymmetric Digital Subscriber Line                |

| ASIC         | Application Specific Integrated Circuit           |

| ASK          | Amplitude Shift Keying                            |

| AWGN         | Additive White Gaussian Noise                     |

| BER          | Bit Error Rate                                    |

| BPSK         | Binary Phase Shift Keying                         |

| СР           | Cyclic Prefix                                     |

| CPLD         | Complex Programmable Logic Device                 |

| dB           | Decibel                                           |

| DFT          | Discrete Fourier Transform                        |

| DSL          | Digital Subscriber Lines                          |

| FDM          | Frequency Division Multiplexing                   |

| FDMA         | Frequency Division Multiplexing Access            |

| FFT          | Fast Fourier Transform                            |

| FPGA         | Field Programmable Gate Array                     |

| HDL          | Hardware Description Language                     |

| IC           | Integrated Circuits                               |

| IDFT         | Inverse Discrete Fourier Transform                |

| IEEE         | Institute of Electrical and Electronics Engineers |

| IFFT         | Inverse Fourier Transform                         |

| ISI          | Intersymbol                                       |

| LAN          | Local Area Network                                |

| LOS          | Line-of-Sight                                     |

| LTE          | Long Term Evolution                               |

|              |                                                   |

| M-FSK | M-ary frequency-shift keying                    |

|-------|-------------------------------------------------|

| M-PSK | M-ary phase-shift keying                        |

| M-QAM | M-ary quadrature amplitude modulation           |

| MIMO  | Multiple-Input and Multiple-Output              |

| OFDM  | Orthogonal Frequency Division Multiplexing      |

| PSK   | Phase Shift Keying                              |

| QAM   | Quadrature Amplitude Modulation                 |

| QPSK  | Quadrature Phase Shift Keying                   |

| RF    | Radio Frequency                                 |

| SNR   | Signal-Noise Ratio                              |

| TTL   | Transistor Transistor Logic                     |

| USB   | Universal Serial Bus                            |

| VDSL  | Very High Bit Rate Digital Subscriber Line      |

| Wi-Fi | Wireless Fidelity                               |

| WiMAX | Worldwide Interoperability for Microwave Access |

| WLAN  | Wireless LAN                                    |

|       |                                                 |

## LIST OF SYMBOLS

| Symbol         | Definition                   |

|----------------|------------------------------|

| $B_W$          | Bandwidth                    |

| $P_b$          | Probability of Error         |

| С              | Speed of Light               |

| $T_s$          | Symbol Duration              |

| $E_s$          | Energy per symbol (Joule)    |

| E <sub>b</sub> | Energy per bit (Joule)       |

| f <sub>c</sub> | Carrier Frequency            |

| $f_s$          | Sampling Frequency           |

| F <sub>s</sub> | Symbol rate (1/sec           |

| λ              | Wavelength                   |

| $\sigma_w^2$   | Gaussian noise variance      |

| N <sub>o</sub> | Noise Power Spectral Density |

| N <sub>b</sub> | Bit per symbol               |

| $P_b$          | Probability of Error         |

#### CHAPTER 1. INTRODUCTION

#### 1.1. Background

The word communication arises from the Latin word **'commūnicāre'**, which means "to share". Communication can be basically defined step for exchange of information. In other words, communication can be defined as information transfer between different points in space or time, where the term information is loosely employed to cover standard formats that we are all familiar with, such as voice, audio, video, data files, web pages, etc. [1]

In the fastest growing of the communication industry, wireless communication technology has rapidly developed. With this development, necessities of requirement for higher data rates and so enlarging demand on band are arisen. Due to capacity requirements, different type of techniques are tried and applied. OFDM (Orthogonal Frequency Domaain Multiplexing) resolves these needs in communication technologies.

#### 1.1.1. Orthogonal Frequency Division Multiplexing (OFDM) Basics

OFDM which is an air-interface technique has become the popular modulation technique for wireless communication systems. Its concept is based on parallel transmission of data over dispersive channels. When the literature is examined, OFDM has been firstly mentioned in 1957. Year-to-year development can be seen from the list which is given below.

#### Year

- 1957 The concept of parallel data transmission **Doelz** *et al.*[2]

- 1966 First OFDM scheme proposed Chang [3]

- 1967 **Saltzberg** studied a multi-carrier system employing Orthogonal QAM of the carriers[4]

- 1970 U.S. Patent on OFDM issued [3]

- 1971 Weinstein & Ebert applied DFT to OFDM modems[5]

- 1980 **Hirosaki** designed a subchannel-based equalizer for an orthogonally multiplexed QAM system [6]

**Keasler** *et al.* described an OFDM modem for telephone networks [7]

- 1985 **Cimini** investigated the feasibility of OFDM in mobile communications [8]

- 1987 Alard and Lasalle employed OFDM for digital broadcasting [9]

- 1991 ANSI ADSL standard [10]

- 1994 ANSI HDSL standard [11]

- 1995 ETSI DAB standard: the first OFDM-based standard for digital broadcasting systems [12]

- 1996 ETSI WLAN standard [13]

- 1997 ETSI DVB-T standard [14]

- 1998 ANSI VDSL and ETSI VDSL standards [15], [16]

ETSI BRAN standard [17]

- 1999 IEEE 802.11a WLAN standard [17]

- 2002 IEEE 802.11g WLAN standard [18]

- 2003 Commercial deployment of FLASH-OFDM commenced [19], [20]

• 2004 ETSI DVB-H standard [21]

IEEE 802.16-2004 WMAN standard [22]

IEEE 802.11n draft standard for next generation WLAN [23]

- 2005 Mobile cellular standard 3GPP Long-Term Evolution (LTE) downlink [24]

- 2007 Multi-user MIMO-OFDM for next-generation wireless [25]

As you seen from the list, even though OFDM's story rely on the old, we can find it in many daily applications such as Wi-Fi, MIMO technique, WiMAX, LTE, DVB standard, DAB broadcast standard and etc.

#### 1.1.2. Field Programmable Gate Array (FPGA) Basics

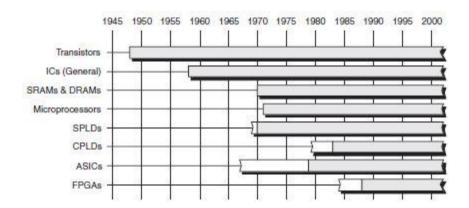

Field programmable gate arrays (FPGAs) are digital integrated circuits (ICs) that contain configurable (programmable) blocks of logic along with configurable interconnects between these blocks[26]. In other words, they have huge array of gates which can be reprogrammed and reconfigured. They are made from silicon, and we can use them to solve any computable problems. The origins of FPGAs are based on transistor technology. Timeline bar approximately indicates related developments from first mentioned to up to date of FPGA technology.

Figure 1: Transistor-Based Technology Timeline [26]

On December 23, 1947, physicists William Shockley, Walter Brattain, and John Bardeen, working at Bell Laboratories in the United States, succeeded in creating the first transistor: a point-contact device formed from germanium. In the following years, BJTs, TTLs, ECLs, and FETs have been pronounced. FETs are often used as abbreviated form of MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistor) which are one of the most basic elements of FPGAs. And in the world of FPGAs, MOSFETs are referred to as gates.

Field programmable gate arrays (FPGAs) can now consist of a million equivalent logic gates and tens of thousands of flip-flops. This means that it is not possible to use traditional methods of logic design involving the drawing of logic diagrams when the digital circuit may contain thousands of gates.[27] FPGAs have traditionally found use in high-speed custom digital applications where designs tend to be more constrained by performance rather than cost.[28]

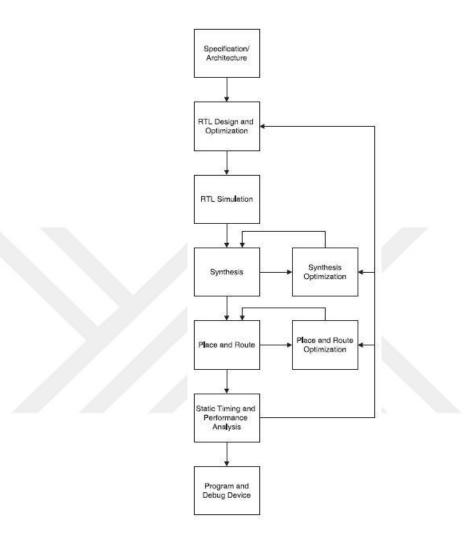

Today digital designers use HDLs (hardware description languages). The most commonly used HDLs are VHDL, Verilog and System Verilog. All of these hardware description languages allow the user to design digital systems by writing a program. The program describes the behavior of the digital circuit. This program can be used to both *simulate* the operation of the circuit and *synthesize* an actual implementation of the circuit in a CPLD, an FPGA, or an application specific integrated circuit (ASIC).[27]

CPLDs and FPGAs are commonly used today, and they have same design flow which consists of the steps below. If we compare them, we can say that FPGAs have more complexity than CPLDs.

Figure 2: FPGA Design Flow [29]

### 1.2. Thesis Overview

The main goal of this thesis is OFDM transmitter and receiver implementation. We used Digilent's Genesys FPGA development board as a hardware. It has Xilinx Virtex-5 FPGA. For develop FPGA, model-based design was chosen. For a modelbased design environment, Xilinx System Generator (Xilinx ISE 14.2) installed MATLAB/Simulink (R2012a) was used. During the model-based design, both native Simulink blocks and Xilinx System Generator blocks was used. The OFDM technique of communication systems evaluated using formula-based calculations, waveformlevel simulation on Simulink and hardware prototyping via FPGA development board.

First of all, in Chapter 2, wireless communication and digital modulation techniques were mentioned briefly. Then, in Chapter 3, OFDM technique was described with its details. In following chapter, in chapter 4, FPGAs and model-based FPGA design via MATLAB Simulink with Xilinx ISE Design Suite were tried to explain step-by-step. Finally, in Chapter 5, designing OFDM transmitter and receiver design with native Simulink blocks and Xilinx specific blocks in MATLAB Simulink was demonstrated. And FPGA implementation of OFDM from Simulink model using System Generator was constructed and results are given.

# CHAPTER 2. WIRELESS COMMUNICATION AND DIGITAL MODULATION TYPES

#### 2.1. An Overview of Wireless Communications

Wireless communications is one of the communication type that is performed and delivered wirelessly. There are different types of wireless communication applications. We can give satellite communication, mobile communication, wireless network communication, infrared communication, and bluetooth communication types as an example for wireless communication.

The first wireless networks were developed in the Pre-industrial age. These systems transmitted information over line-of-sight distances (later extended by telescopes) using smoke signals, torch signaling, flashing mirrors, signal flares, or semaphore flags [30]. The ongoing needs for communication since Pre-industrial age, it has improved day-by-day. After telegraph network which was invented by Samuel Morse in 1838 telephone was invented. Following these events, Italian physicist Guglielmo Marconi who was born in 1874 in Bologna succeeds sending first radio transmission. This event is referred to as a pioneer of wireless communication.

Digital communication systems are becoming increasingly attractive because of the ever-growing demand for data communication and because digital transmission offers data processing options and flexibilities not available with analog transmissions [31]. In other way, digital communication offers the less complexity of communication of during signal processing.

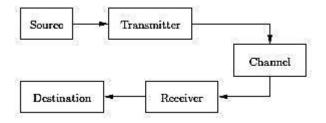

Figure 3: Basic Digital Communication Model

Digital modulation is the process of representing binary information using segments of different sinusoidal waveforms. The parameters that can be adjusted in a sinusoidal wave are its amplitude, frequency and phase [32].

#### 2.2. Digital Modulation Types

The basic purpose of communication is to exchange information as a general. Digital communication systems are communication systems that use digital sequences as an interface between the source and the channel input [33]. This situation is also similar on the receiver side, and we can think of reversing the order of transmitter side.

In digital communication, modulation is a term that is used very frequently. We can define modulation in a general as representation of digital information in terms of analog waveforms. In this form, information can be transferred over the physical channels. In digital communication, the digital data are used, and the data are in the form of a stream of binary data which are 0's and 1's.

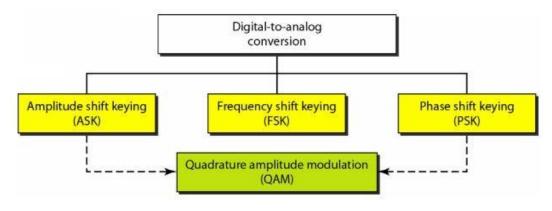

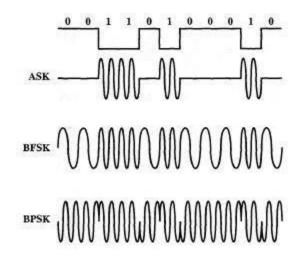

A number of other advantages over the analog modulation are offered by digital modulation. It's including powerful error correction techniques, higher data rates, resistance to channel impairments, more efficient multiple access strategies, and better security and privacy. Digital modulations allow us to transfer a bit stream data through the analog channels. Especially, high level modulation techniques such as MQAM allow much higher data rates in digital modulation as compared to analog modulation with the same signal bandwidth. [30] The most fundamental digital modulation techniques are based on keying, and they are named according to the techniques. These are ASK FSK, PSK and QAM modulation types which are explained below:

Figure 4: Digital Modulation Types

### 2.2.1. ASK (Amplitude Shift Keying)

In Amplitude Shift Keying (ASK), the two binary values are represented by two distictive amplitudes of the carrier frequency. This modulation type can be easily understood with the figure which is given below. Mathematically;

$$s(t) = \begin{cases} A\cos(2\pi f_c t) & 1 \ (binary) \\ 0 & 0 \ (binary) \end{cases}$$

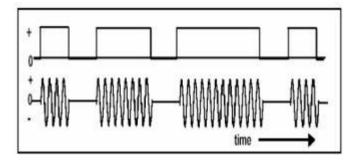

Figure 5: ASK modulation for Digital Data

#### 2.2.2. FSK (Frequency Shift Keying)

The most common form of FSK is binary FSK (BFSK), in which the two binary values are represented by two distinctive frequencies close the carrier frequency. The resulting transmitted signal for one bit time is mathematically explained below.

$$s(t) = \begin{cases} A\cos(2\pi f_1 t) & 1 \ (binary) \\ A\cos(2\pi f_2 t) & 0 \ (binary) \end{cases}$$

#### 2.2.3. PSK (Phase Shift Keying)

In Phase Shift Keying (PSK) or Digital Phase Modulation, the phases of the carrier signals are shifted to represent data. Mathematically;

$$s(t) = \begin{cases} A\cos(2\pi f_c t) & 1 (binary) \\ A\cos(2\pi f_c t + \pi) & 0 (binary) \end{cases} = \begin{cases} A\cos(2\pi f_c t) & 1 (binary) \\ -A\cos(2\pi f_c t) & 0 (binary) \end{cases}$$

Figure 6: ASK, BFSK and BPSK Modulation Types[34]

In Quadrature phase shift keying (QPSK), the carrier varies in terms of phase the carrier undergoes four changes in phase (four symbols) and can thus represent 2 binary bits of data per symbol. There are four possible phase shifts.

Figure 7: QPSK

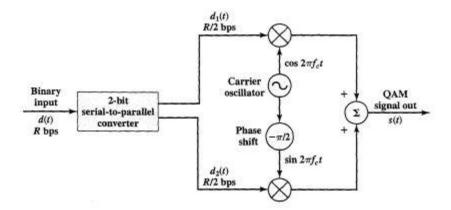

### 2.2.4. QAM (Quadrature Amplitude Modulation)

Quadrature Amplitude Modulation (QAM) is a well-kown analog signaling technique that's used in wireless standards. In QAM, carrier wave is modulated by changing both amplitude and phase. For QAM modulation, we can say that it is a combination of Amplitude Shift Keying (ASK) and Phase Shift Keying (PSK). With QAM modulation, higher data rates can be carried than ASK and FSK.

Figure 8: QAM Modulator [34]

QAM can be expressed as:

$$s(t) = A_I \cos(2\pi f_c t) + A_Q \sin(2\pi f_c t)$$

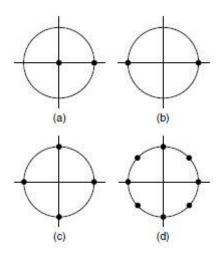

Figure 9: Commonly used QAM (Quadrature Amplitude Modulation) Constellations [35]

**Figure 10:** Signal Constellations of Some Basic Single-Carrier Digital Modulation Techniques a) Binary-ASK b) Binary-PSK c) QPSK d) 8PSK

# CHAPTER 3. ORTHOGONAL FREQUENCY DOMAIN MULTIPLEXING (OFDM)

#### **3.1. Expression of OFDM**

In wireless communication systems technology, OFDM (orthogonal frequency-division multiplexing) has become the popular modulation type. It can be seen as either a modulation technique or a multiplexing technique in literature. This technology has been developed for wideband digital communication, and used for encoding of digital signal of multiple carrier frequencies. In this technique, data is carried with orthogonal sub-carrier signals with different frequencies. Audio broadcasting, DSL Internet Access, Wireless Networks, and in 4G mobile communication systems are using OFDM method.

Frequency division multiplexing (FDM) extends the concept of single carrier modulation by using multiple subcarriers within the same single channel. The evolution of OFDM can be defined as a combination of Frequency Domain Multiplexing (FDM) and Multi-Carrier Modulation/Communication (MCM).

Figure 12: Frequency-Time Representative of an OFDM Signal [36]

Only one sinusoidal wave at all times is used by single-carrier modulation techniques. In the multi-carrier modulation techniques, several sinusoidal waves are transmitted simultaneously. Only one of the three parameters–amplitude, frequency and phase–of the sinusoidal wave are modified by basic single-carrier modulation techniques according to the binary information to be transmitted [32].

Figure 13: Single-Frequency and Multi-Frequency Network [32]

In a classical parallel-data system, the total signal frequency band is divided into N non-overlapping frequency subchannels. Each subchannel is modulated with a separate symbol, and then the N subchannels are frequency multiplexed. It seems good to avoid spectral overlap of channels to eliminate interchannel interference. However, this leads to inefficient use of the available spectrum [37]. With OFDM technique, use of band becomes efficient.

Figure 14: OFDM Spectrum [38]

|                             |        | ā           | DAB        |     | 2                                        | DVB-T                         | 802.11a/g                           | 802.16e-OFDM                            |      |      | 3GPP-LT    | <b>3GPP-LTE EUTRA</b>      | er.   |       |

|-----------------------------|--------|-------------|------------|-----|------------------------------------------|-------------------------------|-------------------------------------|-----------------------------------------|------|------|------------|----------------------------|-------|-------|

| Carrier Frequency<br>(GHz)  | 50.375 | <b>S1.5</b> | <b>S15</b> | ß   | 0.4 -                                    | 0.4 ~ 0.8                     | 2.5, 5.8                            | 2-11                                    |      |      | 1000       | 8                          |       |       |

| Sample Frequency<br>(MHz)   |        |             | 4          |     | 6.8, 8                                   | 6.8, 8, 9.14                  | 20                                  | 8/7*B,<br>7/6*B                         | 1.92 | 3.84 | 7.68       | 15.36                      | 23.04 | 30.72 |

| Bandwidth<br>(MHz)          |        | T           | 1.5        |     | 6, 3                                     | 6, 7, 8                       | 20                                  | 1.5~28                                  | 1.25 | 2.5  | 5          | 10                         | 15    | 20    |

| FFT Size                    | 2048   | 1024        | 512        | 256 | 8192                                     | 2048                          | 5                                   | 256                                     | 128  | 256  | 512        | 1024                       | 1536  | 2048  |

| Used Subcarriers            | 1536   | 768         | 384        | 192 | 6817                                     | 1705                          | 23                                  | 200                                     | 76   | 151  | 301        | 601                        | 901   | 1201  |

| Guardband Ratio             |        | 6           | 0.25       |     | 0.1678                                   | 0.1675                        | 0.1875                              | 0.2185                                  |      |      | ò          | 0.41                       |       |       |

| Subcarrier Spacing<br>(KHz) | F      | R           | 4          | 8   | 1.116 <sup>(1)</sup>                     | 4.464 <sup>(1)</sup>          | <b>212E</b>                         | 125(3)                                  |      |      |            | 5                          |       |       |

| FFT Period<br>(µs)          | 1000   | 500         | 250        | 125 | 896 <sup>(1)</sup>                       | 224 <sup>(1)</sup>            | 3.2                                 | 8 <sup>(3)</sup>                        |      |      | 66         | 66.7                       |       |       |

| Guard Interval<br>(JLS)     | 246    | 123         | 62         | μ   | 224,<br>112,<br>56,<br>28 <sup>(1)</sup> | \$\$\$<br>\$                  | 8.0                                 | 2,<br>1,<br>0.5,<br>0.25 <sup>(3)</sup> |      |      | 14         | 4.67,<br>16.67             |       |       |

| Guard Interval<br>Ratio     |        | 7           | 1/4        |     | 7757                                     | 1/4,<br>1/8,<br>1/16,<br>1/32 | 1/4                                 | 1/4,<br>1/8,<br>1/16,<br>1/32           |      |      | []6<br>[]1 | 9/128,<br>1/4              |       |       |

| Constellation               |        | ğ           | DQPSK      |     | 942                                      | QPSK,<br>16-QAM,<br>64-QAM    | BPSK,<br>QPSK,<br>16-QAM,<br>64-QAM | BPSK,<br>QPSK,<br>16-QAM,<br>64-QAM     |      |      | 973        | QPSK,<br>16-QAM,<br>64-QAM |       |       |

| Maximum Data<br>Rate (bps)  |        | 7           | 1.8M       |     | 31.6                                     | 31.67M <sup>(1)</sup>         | S4M                                 | 104.7M <sup>(2)</sup>                   |      |      | × 10       | > 100M <sup>(3)</sup>      |       |       |

<sup>(1)</sup>; For a 8-MHz channel <sup>(2)</sup>; For a 28-MHz channel <sup>(3)</sup>; For a 20-MHz channel

Figure 15: System Parameters of Several Wireless Communication Standards using the OFDM Technology

The OFDM transmission has the following **advantages**:

• OFDM is an efficient way to deal with multipath; for a given delay spread, the usage complexity is essentially lower than that of a single-carrier system with an equalizer,

• In relatively slow time-varying channels, it is possible to enhance capacity significantly by adapting the data rate per SC according to the signal-to-noise ratio (SNR) of that particular SC,

• OFDM is robust against narrowband interference because such interference affects only a small percentage of the SCs,

• OFDM makes single-frequency networks possible, which is especially attractive for broadcasting applications [37].

On the other hand, OFDM also has some **drawbacks** compared with single carrier modulation:

• OFDM is more sensitive to frequency offset and phase noise,

• OFDM has a relatively large peak-to-average-power ratio, which tends to diminish the power efficiency of the radio frequency RF amplifier [37].

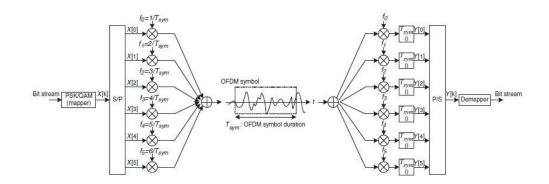

Figure 16: OFDM Transceiver Architecture for QAM [32]

In Figure, on transmitter side, the message bits into a sequence of PSK or QAM symbols are mapped by OFDM transmitter. They will be subsequently converted into N parallel streams. Each of N symbols are carried out by the different subcarrier. This situation is also similar on the receiver side, and we can only think of reverse.

There are a lot of parameter to develop OFDM system, and these parameters are detailed below step-by-step.

#### **3.2.** Orthogonality

In OFDM, all of subscribers are chosen orthogonal each other. Orthogonal is another word for perpendicular. It means that subcarriers are perpendicular in a mathematical sense, allowing the spectrum of each sub-channel to overlap another without interfering with it. The subcarriers are closely spaced and are modulated with low data rates. With orthogonal procedure, sub-channels can be prevented from undesired effects of channels as a crosstalk. Moreover, we can say that the orthogonality technique simplifies the design both the transmitter and receiver sides.

Time-limited complex exponential signals:

$$\{e^{j2\pi f_k}\}_{k=0}^{N-1}$$

Different subcarriers frequencies:

$$f_{k=\frac{k}{T_{sym}}}$$

To make a decision of orthogonality, the integral of their products should equal to zero:

$$\frac{1}{T_{sym}} \int_{0}^{T_{sym}} e^{j2\pi f_{k}t} e^{-j2\pi f_{i}t} dt = \frac{1}{T_{sym}} \int_{0}^{T_{sym}} e^{j2\pi \frac{k}{T_{sym}}t} e^{-j2\pi \frac{k}{T_{sym}}t} dt$$

$$= \frac{1}{T_{sym}} \int_{0}^{T_{sym}} e^{j2\pi \frac{(k-i)}{T_{sym}}t} dt$$

$$= \begin{cases} 1, & k=i \\ 0, & otherwise \end{cases}$$

For discrete systems, equation becomes;

$$t = nT_s = nT_{sym} = \frac{nT_{sym}}{N}, \qquad n = 0, 1, 2, ..., N - 1.$$

Now, equation can be written in the discrete time domain:

$$\frac{1}{N} \sum_{n=0}^{N-1} e^{j2\pi \frac{k}{T_{sym}} nT_s} e^{-j2\pi \frac{k}{T_{sym}} nT_s} = \frac{1}{N} \sum_{n=0}^{N-1} e^{j2\pi \frac{k}{T_{sym}} \frac{nT_{sym}}{N}} e^{-j2\pi \frac{k}{T_{sym}} \frac{nT_{sym}}{N}}$$

$$= \frac{1}{N} \sum_{n=0}^{N-1} e^{j2\pi \frac{(k-i)}{N} \cdot n}$$

$$= \begin{cases} 1, & k = i \\ 0, & otherwise \end{cases}$$

#### 3.3. Concept of FFT and IFFT

Many practical problems in signal analysis involve either infinitely long or very long signals where the Fourier series is not appropriate. For these cases, the Fourier transform (FT) and its inverse (IFT) has been developed. This transform has been used with great success in virtually all quantitative areas of science and technology where the concept of frequency is important. [39]

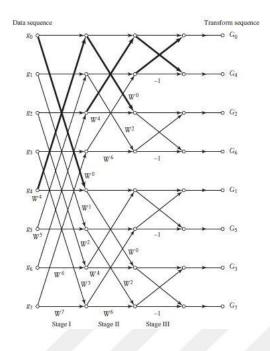

The Fast Fourier Transform (FFT) and its inverse (IFFT) are very important algorithms in signal processing, software-defined radio, and the most promising modulation technique; Orthogonal Frequency Division Multiplexing (OFDM). The Fast Fourier Transform (FFT) algorithm has a long history. Its modern discovery is attributed to Cooley and Tukey in 1965. Details can be available from the publication which is 'An Algorithm for the Machine Calculation of Complex Fourier Series (1992)'.

Figure 17: FFT Algorithm for Parallel Data

#### 3.3.1. Discrete Fourier Transform (DFT)

The Discrete Fourier Transform (DFT) is a specific kind of Fourier transform. A French physicist and mathematician, Joseph Fourier, formalized the notion of the spectrum in the early nineteenth century. The Fourier transform of a real-valued or complex function of the real-variable t is defined by

$$x(t) \stackrel{FT}{\leftrightarrow} X(\omega)$$

$$X(\omega) = \int_{-\infty}^{\infty} x(t) e^{-j\omega t} dt$$

In OFDM, Discrete Fourier Transform (DFT) is used for modulating each subchannel onto the appropriate carrier on transceiver side. Before FFT processing modulated digital signals are mapped to particular sub-carrier (serial-to-parallel conversion).

$$x_n \stackrel{DFT}{\longleftrightarrow} X_k$$

$$X_{k} = \sum_{n=0}^{N-1} x_{n} W_{N}^{-kn}$$

$$= \sum_{n=0}^{N-1} x_{n} e^{-jk\frac{2\pi}{N}n} \qquad k = 0, \dots, N-1.$$

In the Discrete Fourier transform (DFT), both the input and the output consist of sequences of numbers defined at uniformly spaced points in time and frequency, respectively. [40]

In Simulink, the FFT block computes the fast Fourier transform (FFT) across the first dimension of an N-D input array.

Figure 18: Simulink FFT Block

#### **3.3.2.** Inverse Discrete Fourier Transform (IDFT)

In OFDM, before IFFT processing modulated digital signals are mapped to particular sub-carrier (serial-to-parallel conversion). Then, inverse Discrete Fourier Transform (iDFT) are applied;

$$X_k \stackrel{DTFT}{\longleftrightarrow} x_n$$

$$x_n = \frac{1}{N} \sum_{n=0}^{N-1} X_k W_N^{-kn}$$

In Simulink, The IFFT block computes the inverse fast Fourier transform (IFFT) across the first dimension of an N-D input array.

#### Figure 19: Simulink IFFT Block

Figure 20: IFFT in Transmitter Side and FFT in Receiver Side

# 3.4. Serial to Parallel Conversion

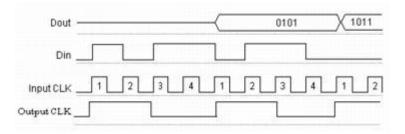

The Serial to Parallel step takes a series of inputs of any size and creates a single output of a specified multiple of that size. The input series can be ordered either with the most significant word first or the least significant word first.

Figure 21: Serial to Parallel Conversion

#### 3.5. Parallel to Serial Conversion

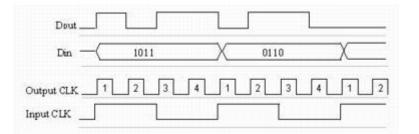

In OFDM, parallel to serial conversion is used for summing all subcarriers and combining them into one signal. Input word is split into N time-multiplexed output words where N is the ratio of number of input bits to output bits. The order of the output can be either least significant bit first or most significant bit first (depends on application).

Figure 22: Parallel to Serial Conversion

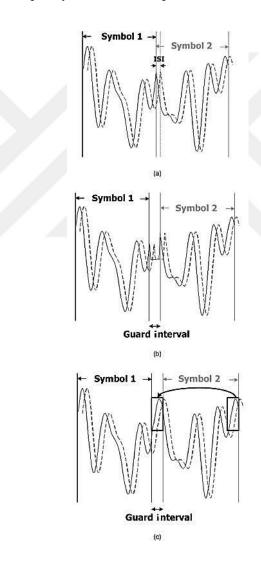

#### **3.6.** Guard Interval / Cyclic Prefix

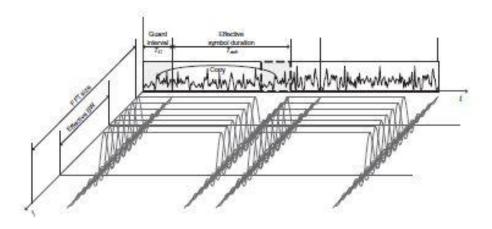

Usually adding cyclic prefix (CP) has two purposes that are eliminate the intersymbol interference (ISI) and inter-channel interference (ICI) [41]. The Cyclic Prefix or Guard Interval is a periodic extension of the last part of an OFDM symbol that is added to the front of the symbol in the transmitter, and is removed firstly at the receiver side before demodulation [38].

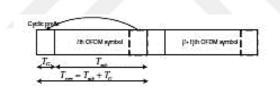

Figure 23: OFDM Symbol with Cyclic Prefix

To preserve the orthogonality of the subcarriers and the independence of subsequent OFDM symbols, Guard Interval (GI) was introduced. The guard interval, a cyclic prefix, is a copy of the last part of the OFDM symbol, which is transmitted before the so-called effective part of the symbol [37]. If cyclic prefix is not inserted in the guard interval, received symbol represents linear convolution and intercarrier interference (ICI) is seen after FFT operation by the receiver [42]. Because of that, after IFFT operation, Cyclic Prefix added.

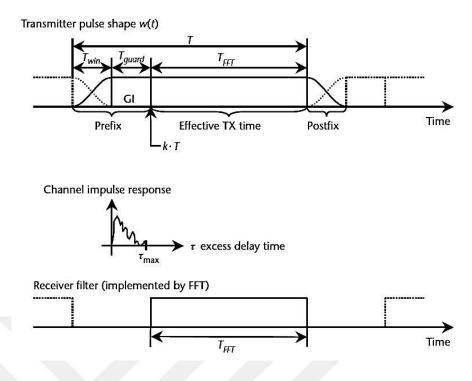

Figure 24: Time / Frequency Domain Description of OFDM Symbols with Cyclic Prefix

Figure 25: (a) Illustration of ISI due to multipath delay; (b) zero-padding guard interval to avoid ISI; (c) guard interval with cyclic prefix to eliminate ISI and ICI [32]

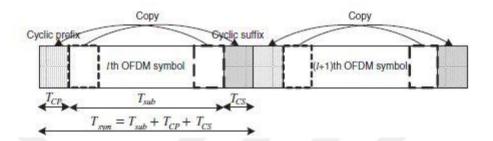

#### 3.7. Cyclic Suffix

Cyclic suffix (CS) is a cyclic extension of the OFDM system. It is diverse from CP. CS is the copy of the head part of an effective OFDM symbol, and it is inserted at the end of the symbol [43]. With both CP and CS, we can suppress the ISI effect of the multipath channel.

Figure 26: OFDM symbol with both Cyclic Prefix (CP) and Cyclic Suffix (CS) [43]

## 3.8. Windowing

Due to the side lobes of its FT (Fourier Transform) being a sinc function, a rectangular pulse has a very large bandwidth. For reducing the level of these side lobes windowing is a well-known technique. Also, it reduces the signal power transmitted out of band. During its effective period, signal must not be influced by the applied in an OFDM system.

Figure 27: Cyclic Extension and Windowing of the OFDM Symbol

#### **3.9.** Channel Models

Between transmitter and receiver, environement can be defined as channel. On channel transmission system are influenced by reflection, refraction and scatter. In theoretical model, there are some methods. In the thesis, AWGN, Rayleigh Fading and Rician Fading were used to model the communication channel.

## 3.9.1. Additive White Gaussian Noise (AWGN)

Additive White Gaussian Noise is the channel which is one of the simplest mathematical models for various physical communication channels, including wirelines and some radio channels. It is a noise that affects the transmitted signal when it passes through the channel.

#### **3.9.2.** Multipath Fading

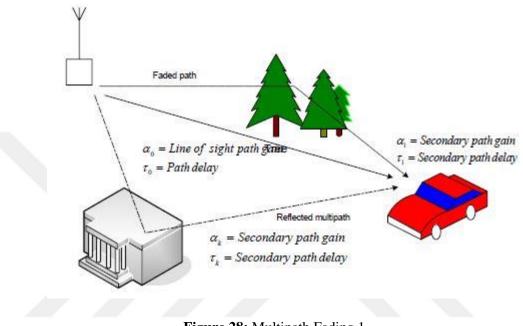

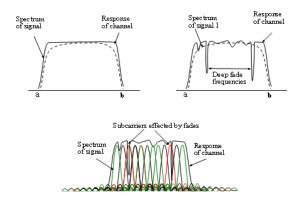

The term fading, means rapid fluctuations of the amplitudes, phases, or multipath delays of a radio signal. In ideal channel, the transmitted signal passes via the channel and go to the receiver side. In receiver side, the signal is demodulated with a specific algorithm to get representation of the message signal which is transmitted.

Figure 28: Multipath Fading 1

In practice, this scenario cannot be fully observed especially receiver side. The receiver side, our signal includes of a mixture of reflected, attenuated, diffracted and refracted signals. In OFDM, ISI and multipath fading effects have been minimized by sending data in parallel subcarriers and at a low data rate [44].

Figure 29: Multipath Fading 2

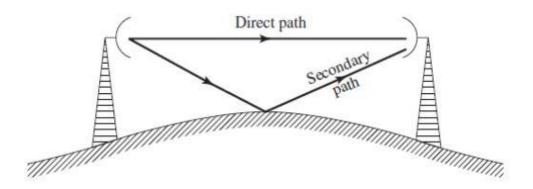

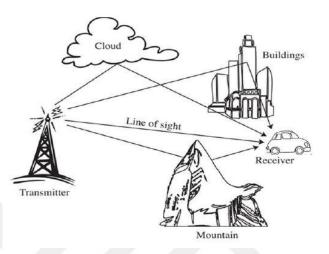

In wireless telecommunications, multipath is the propagation that results in radio signals reaching the receiving antenna by two or more paths. These paths may be the result of reflections from buildings, mountains or other reflective surfaces including water, etc. that may be adjacent to the main path.

Figure 30: Multipath Propagation Effects

Propagation in a mobile radio channel is determined mainly by its multiple natures. The path from the transmitter side to the receiver side either has also reflections and some of obstructions. Because of the signal reaches the receiver from many different routes, each of these signals has a slightly different delay and gain. The time delays result in phase shifts which added to main signal.

Figure 31: Fading Effect

#### **3.9.2.1.Rayleigh Fading**

Rayleigh fading is observed when no LOS, path exists in between transmitter and receiver, but only have indirect path than the resultant signal received at the receiver will be the sum of all the reflected and scattered waves. In other words, where the magnitudes of the signals arriving by the various paths have a distribution known as the Rayleigh distribution, this is known as Rayleigh fading.

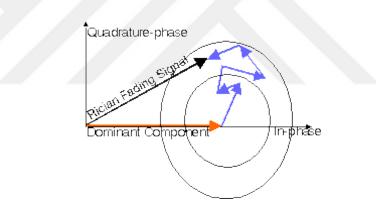

#### **3.9.2.2.Rician Fading**

Rician Fading occurs when there is a LOS (Line-of-Sight) as well as the non-LOS path in between the transmitter and receiver, i.e. the received signal comprises on both the direct and scattered multipath waves [45].

Figure 32: Phasor Diagram of Rician Fading

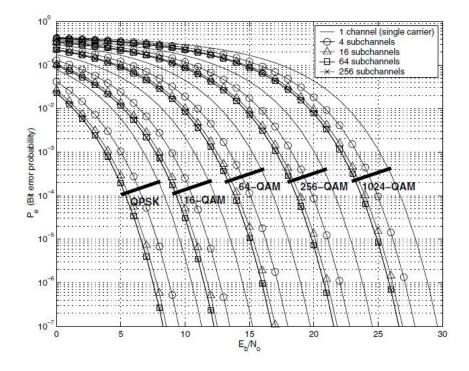

#### 3.10. Performance of OFDM System

OFDM performance evaluated with those channels in terms of bit-error rates (BERs) and signal-to-noise ratios (SNRs) calculation over AWGN and multipath fading channels.

#### 3.10.1. Bit Error Rate (BER) Measurement

The performance analysis is enable for modern digital communications systems. With the end-to-end performance measurements, our system can become more stable. The measure of that performance is usually Bit Error Rate (BER), which quantifies the reliability of the entire system from "bits in" to "bits out", including the electronics, antennas and signal path in between [46]. In our Simulink model which includes Xilinx blocks and Simulink blocks, BER calculated with native Simulink block which is shoven below.

Figure 33: Simulink Error Rate Calculation Block

It compares input data from a transmitter with input data from a receiver, and is calculating the BER.

$$\mathbf{BER} = \frac{\text{Bits in Error}}{\text{Total bits received}}$$

BER can also be defined in terms of the probability of error (POE or  $P_e$ ) [30] and expressed generally as

$$P_e = \frac{1}{2}(1 - erf) \sqrt{\frac{E_b}{N_0}}$$

For M-ary QAM, Bit Error Probability (Probability of Bit Error) becomes:

$$P_e = \frac{\sqrt{M} - 1}{\sqrt{M} \log_2 \sqrt{M}} \operatorname{erfc}\left(\sqrt{\frac{3 \log_2 M E_b}{2(M-1) N_0}}\right)$$

For M=4, equation reduces to the Bit Error Probability of QPSK (for single-carrier):

$$P_e = \frac{1}{2} erfc \left( \sqrt{\frac{E_b}{N_0}} \right)$$

For M-ary QAM with N subchannels,  $P_e$  becomes:

$$P_{e} = \frac{\sqrt{M} - 1}{\sqrt{M} \log_{2} \sqrt{M}} erfc \left( \sqrt{\frac{(2^{\sqrt{N}} - 1)}{2^{\sqrt{N} - 1}}} \frac{3 \log_{2} M E_{b}}{2 (M - 1) N_{0}} \right)$$

For M=4 (QPSK), equation becomes,  $P_e$  becomes:

$$P_e = \frac{1}{2} \operatorname{erfc}\left(\sqrt{\frac{\left(2^{\sqrt{N}} - 1\right)}{2^{\sqrt{N}-1}}} \frac{E_b}{N_0}\right)$$

Figure 34: Theoretical Bit Error Probability vs.  $E_b/N_0$  for M-QAM-N

# 3.10.2. Signal to Noise Ratio (SNR)

SNR is the ratio of the received signal to the noise in the frequency range. SNR is inversely related to BER, that is high BER causes low SNR.

$$SNR = \frac{Signal Power}{Noise Power} = \left(\frac{F_s}{B}\right) \left(\frac{E_s}{N_0}\right) = N_b \left(\frac{F_s}{B}\right) \left(\frac{E_b}{N_0}\right)$$

- $F_s$ : Symbol rate (1/sec)

- *B*: Bandwidth (Hz = 1/sec)  $\geq F_s$

- $N_0$ : Noise power spectral density

- $E_s$ : Energy per symbol (Joule)

- $E_b$ : Energy per bit (Joule)

- $N_b$ : Bit per symbol

# CHAPTER 4. FPGAs & DIGILIENT'S GENESYS VIRTEX-5 DEVELOPLMENT BOARD

Todays, field programmable gate arrays (FPGAs) are using many areas which ares Aerospace, Medical, Automotive, Broadcast, Consumer Electronics, Industrial, Digital Signal Processing, Communication. Although there are many produces of FPGAs, two companies which are Xilinx and Intel (Altera) taking on this role more. They are two major manufacturers which are Xilinx and Intel (Altera).

In communication systems, DSPs and FPGAs are using generally. Reasons of for preference of FPGAs are their high performance data processing ability. DSP performance is derived from the FPGA's ability to construct highly parallel architectures for processing data. In contrast with a microprocessor or DSP processor, where performance is tied to the clock rate at which the processor can run, FPGA performance is tied to the amount of parallelism that can be brought to bear in the algorithms that make up a signal processing system.[47]

In our thesis, developed model was impelemented on Digilent's Genesys Virtex-5 (Xilinx) FPGA board.

#### 4.1. Digilent Genesys<sup>™</sup> Virtex-5 FPGA Development Board

The Genesys circuit board is a complete, ready-to-use digital circuit development platform based on a Xilinx Virtex-5 LX50T. The large on-board collection of high-end peripherals, including Gbit Ethernet, HDMI Video, 64-bit DDR2 memory array, and audio and USB ports make the Genesys board an ideal host for complete digital systems, including embedded processor designs based on Xilinx's MicroBlaze. [48]

Figure 35: Digilent's Genesys Virtex-5 FPGA Development Board

# 4.2. Digilent Genesys<sup>™</sup> Virtex-5 FPGA Development Board Feature

- Xilinx Virtex 5 LX50T FPGA, 1136-pin BGA package,

- 256Mbyte DDR2 SODIMM with 64-bit wide data,

- 10/100/1000 Ethernet PHY and RS-232 serial port,

- Multiple USB2 ports for programming, data, and hosting,

- HDMI video up to 1600x1200 and 24-bit color,

- AC-97 Codec with line-in, line-out, mic, and headphone,

- Real-time power monitors on all power rails,

- 16Mbyte StrataFlash<sup>TM</sup> for configuration and data storage,

- Programmable clocks up to 400MHz,

- 112 I/O's routed to expansion connectors,

- GPIO includes eight LEDs, two buttons, two-axis navigation switch, eight slide switches and a 16x2 character LCD.

#### 4.3. Board Configuration

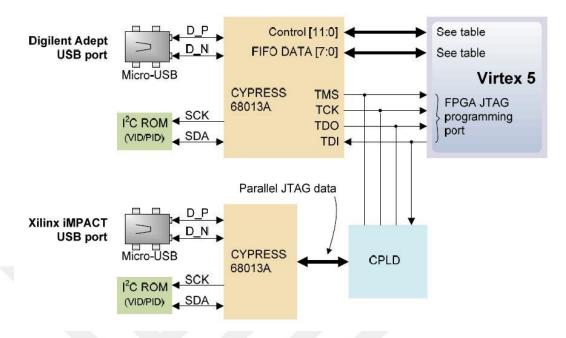

Figure 36: Board Programming Configuration

### 4.4. Adept System

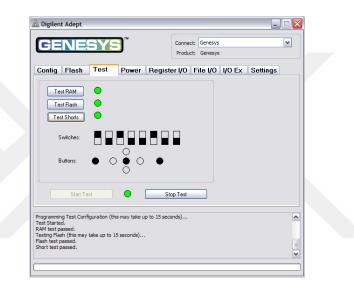

The Digilent Adept System is a collection of application programs, runtime libraries and drivers that allow users to interact programmatically with various Digilent products. The Digilent Adept Runtime contains the shared libraries and drivers that support the applications programs, and the Digilent Adept SDK provides the link libraries and documentation needed to write applications programs to work with the Adept System [49].

| 🖄 Digilent Adept                                   |                   | 6 <u>37</u> 0)       | × |

|----------------------------------------------------|-------------------|----------------------|---|

|                                                    | Connect: Product: | lo Devices Connected | ~ |

| Settings                                           |                   |                      |   |

| Application Settings                               |                   |                      |   |

| Auto Initailize SC                                 |                   |                      |   |

| Hide Status Window                                 |                   |                      |   |

| Slow Programming Speed                             |                   |                      |   |

|                                                    |                   |                      |   |

| Clear Status Window                                |                   |                      |   |

| Clear File History                                 |                   |                      |   |

| Device Manager                                     |                   |                      |   |

| Device Manager                                     |                   |                      |   |

|                                                    |                   |                      |   |

|                                                    |                   |                      |   |

|                                                    |                   |                      |   |

| ===== Digilent Adept =====<br>Adept System Rev 2.7 |                   |                      |   |

| Adept Runtime Rev 2.16                             |                   |                      |   |

| Adept Application Rev 2.4.2<br>Copyright © 2010    |                   |                      |   |

|                                                    |                   |                      |   |

|                                                    |                   |                      |   |

Figure 37: Adept Screen before Connection is Established

The Genesys board includes two USB peripheral ports – one for Adept software and another for Xilinx's iMPACT software. Either port can program the FPGA and StrataFlash, but Adept offers a simplified user interface and many additional features such as automated board test and user-data transfers. The Adept port is also compatible with iMPACT, if the Digilent Plug-In for Xilinx Tools is installed on the host PC (download it free from the Digilent website). [48]

| GENESYS                                                                                                                       | Connect: Genesys<br>Product: Genesys        |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| onfig Flash Test P                                                                                                            | Power Register I/O File I/O I/O Ex Settings |

| FPGA<br>XC5VLX50T                                                                                                             | Browse Program                              |

|                                                                                                                               |                                             |

|                                                                                                                               |                                             |

|                                                                                                                               |                                             |

|                                                                                                                               | Initialize Chain                            |

| ading board information<br>tializing Scan Chain                                                                               |                                             |

|                                                                                                                               |                                             |

| and information loaded.<br>and information loaded.<br>and device ID: 82a96093<br>tialization Complete.<br>Device 1: XC5VLX50T |                                             |

Figure 38: Adept Screen after Connection is Established

Adept's can be used fort o run automated board tests for our board. From Digilent USB2 interface, connection is possible between PC and the device. Adept automatically recognizes the Genesys board and presents a graphical interface with tabs for each of these applications [48].

With this interface, we can verify that our board works. After connection with cable via USB port, we can check on board 256Mbyte DDR2 RAM, flash memories, short circuits, 16 slide switches and 16 push buttons.

Figure 39: Adept Test Window

# CHAPTER 5. MATHWORKS' MATLAB/SIMULINK AND XILINX'S SYSTEM GENERATOR FOR DSP

Large-scale systems are all around and exist in diverse fields such as complex chemical processes, biomedical systems, social economic systems, transportation systems, ecological systems, electrical systems, mechanical systems, and aeronautical and astronautics systems[50]. With conventional techniques, all these large and complex systems are difficult to model. Hence, these systems can be decoupled or partitioned into suitable numbers of interconnected subsystems to reduce their complexity for modeling purposes [50]. Similar to mentioned purposes above, MATLAB (R2012a) environment was selected to develop all of models in thesis.

## 5.1. MathWorks' MATLAB/Simulink

MATLAB which developed by MathWorks is the software. Users can analyze data, can develop algorithms and can create mathematical models. It offers a wide range of usage areas. For analyze digital signals, MATLAB is a most handy tool.

Simulink also developed by MathWorks and integrated with MATLAB. It is graphical programming software which offers system-level design, simulation, automatic code generation, and continuous test and verification of embedded systems. It also supports model-based hardware design using system generator (Xilinx). In thesis, it used for model-based FPGA design.

Figure 40: MATLAB - Simulink and Its Blockset Screen

## 5.2. Xilinx ISE Design Suite and System Generator

Xilinx is one of Technology Company which is an American origin. This company has Xilinx ISE Design Suite is Xilinx's software development environment. It offers a comprehensive set of familiar and powerful tools, libraries and methodologies. To design model-based FPGA, Xilinx ISE Design Suite should be installed to user PC. During installation of Xilinx ISE Design Suite, there are options which depend on what you want from software. To install System Generator, Vivado System Edition option should be chosen during installation of Xilinx ISE Design Suite. To design model-based FPGA from MATLAB/Simulink, development environment which can be Linux or Windows should include System Generator. System generator is a DSP design tool from Xilinx that enables the use of Mathworks Model-Based Simulink for FPGA design.

| cts to Install  PPACK  ign Suite Logic Edition + Vivado Design Edition  ign Suite Embedded Edition + Vivado Design Edition  ign Suite DSP Edition + Vivado System Edition  ign Suite System Edition + Vivado System Edition  e Development Kit - Standalone Installation  otumentation Navigator - Standalone Installation  ed : 17871 MB                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e Development Kit - Standalone Installation<br>Ns - Standalone Installation<br>ocumentation Navigator - Standalone Installation<br>ed : 17871 MB                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| E Design Suite System Edition + Vivado System Edition<br>contains everything you need to do a complete system design. It includes the<br>Vivado System Edition toola, ISE Design Suite Logic Edition, the Embedded<br>t (EDK), System Generator for DSP and Documentation Navigator.<br>Edition is a superset of Vivado Design Edition with the same front-to-back<br>dded design support, Vivado High-Level Synthesis and System Generator for |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 41: Xilinx ISE Design Suite Installation Screen

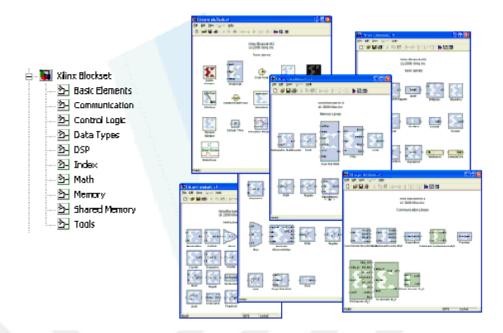

Xilinx System Generator that facilitates FPGA hardware design pioneered the idea of compiling an FPGA program from MATLAB and Simulink model. It provides system modeling and automatic code generation from MATLAB and Simulink. During the design of Simulink model, system generator blocksets can be used like other Simulink blocksets. Moreover, designer can also use both Simulink native blocks and Xilinx System Generator blocks at the same time. The blocks provide abstractions of mathematical, logic, memory, and DSP functions that can be used to build sophisticated signal processing systems [47]. User can design hardware using these System Generator Blocks.

Figure 42: Simulink System Generator Blocksets [47]

Xilinx FPGAs or RTL design methodologies are not required when using System Generator. Designs are captured in the Simulink modeling environment using a Xilinx-specific block set. All of the downstream FPGA implementation steps including RTL synthesis and Place and Route are automatically performed to produce an FPGA programming bitstream. [51]

#### 5.3. MATLAB/Simulink & System Generator Configuration

In this thesis, Xilinx's FPGA which is Virtex-5 were used as said before. To design model-based FPGA, Mathworks' Simulink environment was used with System Generator blocks. Used software to design hardware should be selected with suitable versions. Installing exact versions of software is one the most important step of taking a short lead. With the wrong versions of Xilinx ISE Design Suite and MATLAB, designing can be incomprehensible. They must also be compatible with the hardware to be used. As mentioned, Genesys Virtex-5 development board was used as hardware; for software Xilinx ISE Design Suite 14.2 and MATLAB 2012a were used. To configure Xilinx ISE Design Suite and Matlab softwares, MATLAB should be

installed first, and then Xilinx ISE Design Suite should be installed. During installing Xilinx ISE Design Suite, from configuration window which is 'Select a MATLAB installation for System Generator', actual MATLAB version must be selected, and then configuration can be completed.

| MATLAB Version | Xilinx Suite | Status         | Location                       |  |

|----------------|--------------|----------------|--------------------------------|--|

| 🗏 📣 R2011b     | ids 👻        | Not Configured | C:\Program Files\MATLAB\R2011b |  |

| 🖉 📣 R2012b     | IDS 👻        | 😝 Configured   | C:\Program Files\MATLAB\R2012b |  |

|                |              |                |                                |  |

|                |              |                |                                |  |

|                |              |                |                                |  |

Figure 43: MATLAB Configuration Window of System Generator

# 5.4. Xilinx Blocksets

# 5.4.1. Organization of Blockset Libraries

There are 12 different types of libraries.

| Library                 | Description                                                         |

|-------------------------|---------------------------------------------------------------------|

| Index                   | Every block includes index in the Xilinx Blockset.                  |

| AXI4 Blocks             | This library Includes every block the supports tjhe AXI4 Interface. |

| Basic Element<br>Blocks | This library includes standard building blocks for digital logic.   |

| Communication  | This library commonly used in digital communications systems          |